# Руководство пользователя по работе с программным обеспечением X-CAD

Предварительное описание

5400TC015

## Оглавление

| ВВЕДЕНИЕ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| МАРШРУТ ПРОЕКТИРОВАНИЯ НА ОСНОВЕ ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ∠   |

| СТРУКТУРА ПРОГРАММНЫХ ДИРЕКТОРИЙ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7   |

| ЗАПУСК ПРОГРАММЫ В КОНСОЛЬНОМ РЕЖИМЕ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ε   |

| ВХОДНЫЕ ДАННЫЕ ПРОГРАММЫ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13  |

| БИБЛИОТЕКИ ЭЛЕМЕНТОВ ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16  |

| ИСПОЛЬЗОВАНИЕ КОНТАКТНЫХ ПЛОЩАДОК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17  |

| ФАЙЛ РАЗМЕЩЕНИЯ КОНТАКТНЫХ ПЛОЩАДОК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21  |

| ИСПОЛЬЗОВАНИЕ ИМЕН КОНТАКТНЫХ ПЛОЩАДОК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24  |

| ВЫПОЛНЕНИЕ СТАТИЧЕСКОГО ВРЕМЕННОГО АНАЛИЗА                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25  |

| ВЫХОДНЫЕ ДАННЫЕ ПРОГРАММЫ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41  |

| ПРИМЕРЫ ЗАПУСКА ПРОГРАММЫ В КОНСОЛЬНОМ РЕЖИМЕ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44  |

| TCL ИНТЕРФЕЙС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45  |

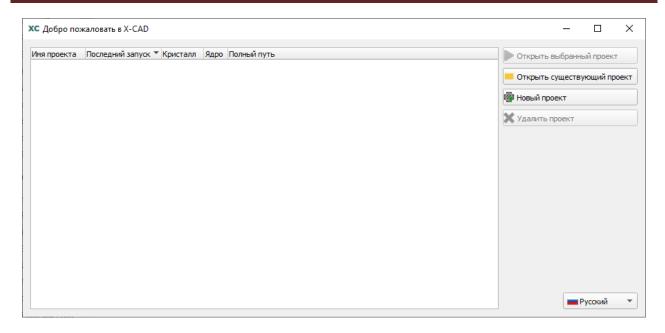

| ГРАФИЧЕСКИЙ ИНТЕРФЕЙС X-CAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48  |

| ИСПОЛЬЗОВАНИЕ ВНЕШНИХ ПРОГРАММ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73  |

| Icarus Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74  |

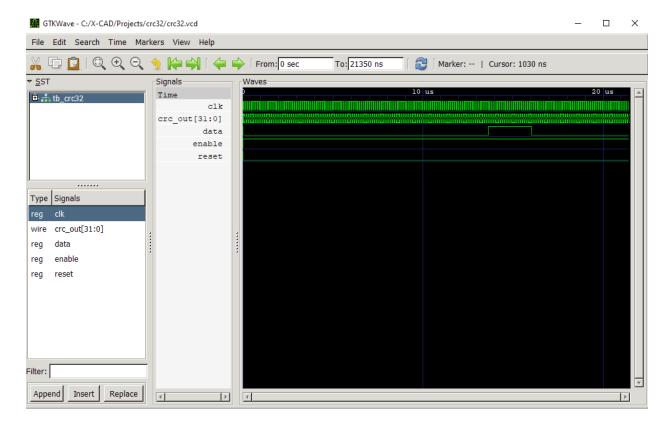

| GTK Wave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81  |

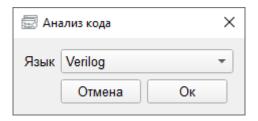

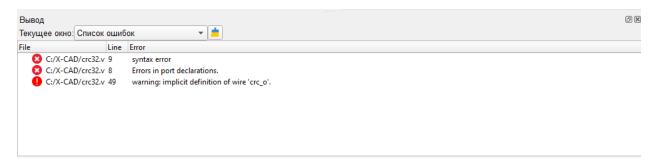

| Анализатор HDL-описаний                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82  |

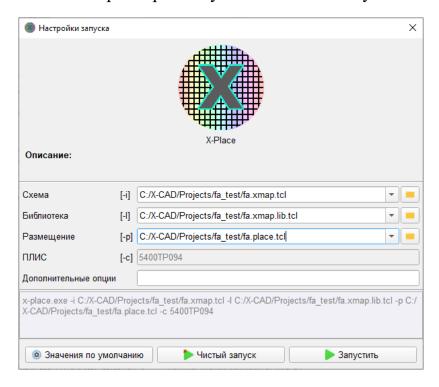

| ИНТЕРФЕЙС ТОПОЛОГИЧЕСКОГО РЕДАКТИРОВАНИЯ X-PLACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83  |

| ИНТЕРФЕЙС ПЛАНИРОВКИ КРИСТАЛЛА FLOORPLANNER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 99  |

| Использование полученного размещения                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 110 |

| Due personne de la companya del companya de la companya del companya de la compan | 440 |

### ВВЕДЕНИЕ

Программный пакет X-CAD предназначен для автоматизации этапов логического синтеза, размещения элементов и трассировки межсоединений микросхем, проектируемых на базе программируемых логических интегральных схем (ПЛИС).

В состав пакета программных средств входят:

- интерфейсные программы на языке C++, обеспечивающие загрузку схемной и топологической информации из базы данных САПР Cadence в форматах CDL, GDS-II.

- Программы на языке C++, интегрированные с языком управления заданиями Tcl и обеспечивающие отображение проектируемой пользовательской схемы на базис элементов библиотеки ПЛИС, а также реализующие прохождение полного маршрута топологического проектирования, состоящего из автоматических процедур планировки, размещения и трассировки межсоединений.

- Скрипты на языке Tcl для поддержки функционирования интерфейса программы X-CAD и управления процессом конфигурирования ПЛИС.

- Библиотеки стандартных элементов в формате Liberty для автоматического синтеза проектных решений средствами Design Compiler (Synopsys), RTL Compiler (Cadence), Genus (Cadence) или Yosys Open SYnthesis Suite (Yosys).

Версия 0.1

## 1. Характеристики ПЛИС

| Шифр ПЛИС                      | 5400TC015 |

|--------------------------------|-----------|

| Параметры                      | 5400TC015 |

| Тех. процесс, нм               | 180       |

| Емкость, ЛЭ                    | 1104      |

| Количество стандартных ЯВВ, шт | 93        |

| Количество тактовых ЯВВ, шт    | 4         |

- 2. Совместимость со сторонним программным обеспечением:

- Cadence Encounter RTL Compiler, Cadence Genus Synthesis Solution,

Cadence Spectre Simulation Platform;

- Synopsys Design Compiler, Synopsys HSPICE;

- Yosys Open SYnthesis Suite;

- Icarus Verilog;

- OSS CVC Simulator.

- 3. Поддерживаемые языки описания аппаратуры:

- Verilog 2005 (стандарт IEEE 1364-2005).

- 4. Системные требования:

- Операционная система Windows 7 или выше;

- Операционная система Red Hat 6 \ Cent OS 6 или выше;

- Оперативная память: 8 Гб;

- Свободное место на жестком диске: 4 Гб;

- Наличие видео драйвера с поддержкой спецификации OpenGL 2.0.

#### МАРШРУТ ПРОЕКТИРОВАНИЯ НА ОСНОВЕ ПЛИС

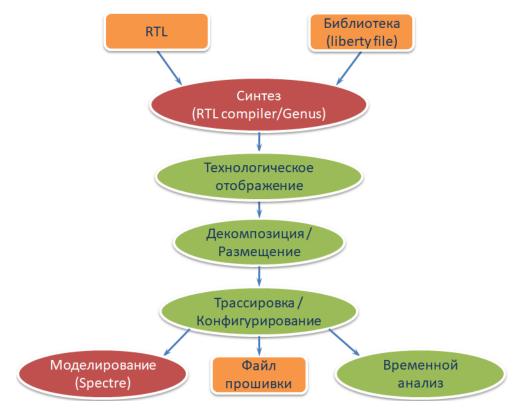

Программные средства X-CAD обеспечивают возможность интеграции с существующим коммерческим ПО (при наличии) для выполнения логического синтеза и моделирования общего назначения от компаний Cadence и Synopsys, а также со свободно распространяемым ПО Yosys Open Synthesis Suite. На рисунке 1 изображен маршрут, обеспечивающий интеграцию средств САПР компании Cadence:

- загрузка файла библиотеки стандартных элементов ПЛИС и HDL описания проектируемой пользовательской схемы в программу логического синтеза RTL Compiler / Genus;

- 2) полученное схемное описание передается в подпрограмму САПР для технологического отображения, размещения и трассировки, после чего происходит проверка проекта на быстродействие с помощью выполнения статического временного анализа (СВА) и моделирования схемы в симуляторе Cadence Spectre;

- 3) в результате работы САПР генерируется файл прошивки ПЛИС.

Рисунок 1 – Маршрут проектирования на ПЛИС с использованием ПО Cadence

Версия 0.1

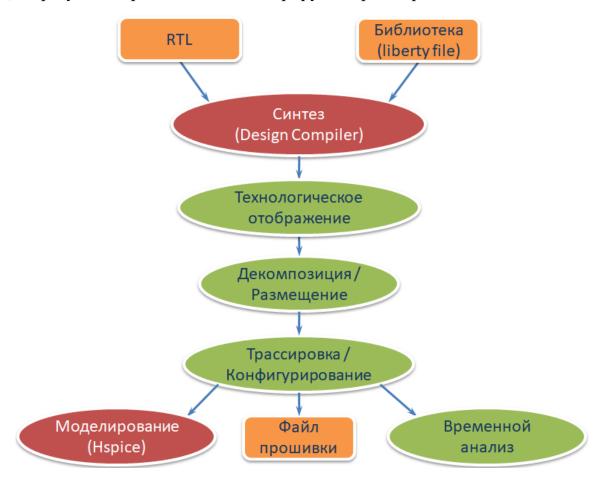

На рисунке 2 приведен аналогичный маршрут, обеспечивающий интеграцию с САПР компании Synopsys:

- загрузка файла библиотеки стандартных элементов ПЛИС и HDL описания проектируемой пользовательской схемы в программу логического синтеза Synopsys Design Compiler;

- 2) полученное схемное описание передается в подпрограмму САПР для технологического отображения, размещения и трассировки, после чего происходит проверка проекта на быстродействие с помощью выполнения статического временного анализа и моделирования схемы в симуляторе HSpice;

- 3) в результате работы САПР генерируется файл прошивки.

Рисунок 2 — Маршрут проектирования на ПЛИС с использованием ПО Synopsys

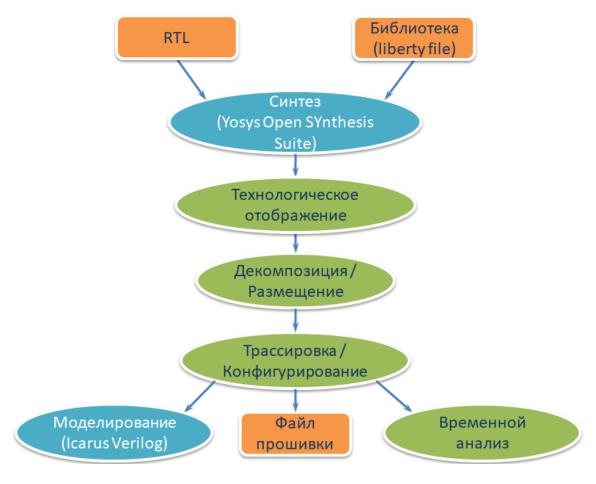

На рисунке 3 приведен маршрут, обеспечивающий интеграцию со свободно распространяемым ПО Yosys Open SYnthesis Suite:

- 1) загрузка файла библиотеки стандартных элементов ПЛИС и HDL описания пользовательской схемы в программу логического синтеза Yosys;

- 2) полученное схемное описание передается в подпрограмму САПР для технологического отображения, размещения и трассировки, после чего происходит проверка проекта на быстродействие с помощью выполнения статического временного анализа и моделирования схемы в симуляторе Icarus Verilog;

- 3) в результате работы САПР генерируется файл прошивки.

Рисунок 3 – Маршрут проектирования на ПЛИС с использованием ПО Yosys

# СТРУКТУРА ПРОГРАММНЫХ ДИРЕКТОРИЙ

Структура директории программы X-CAD:

X-CAD # домашняя директория

bin # директория исполняемых модулей

xcore.exe # модуль для запуска XCORE

xcad.exe # модуль для запуска XCAD, графического

интерфейса САПР

xplace.exe # модуль для запуска XPLACE

xmap.exe # модуль для запуска XMAP

xsta.exe # модуль для запуска XSTA

src # директория с исходными файлами

/data  $\# \phi$ айлы кон $\phi$ игурации ПЛИС

/libraries # библиотеки для работы с ПЛИС

/scripts # управляющие скрипты

/docs # документация

lib # библиотеки tcl/tk

tools # программные модули Yosys, IcarusVerilog, GTK Wave, CVC

Версия 0.1

#### ЗАПУСК ПРОГРАММЫ В КОНСОЛЬНОМ РЕЖИМЕ

Консольный режим программы выполняется с помощью управляющего скрипта на языке Tcl. Команда запуска из системной консоли имеет следующий вид:

<PATH>/bin/xcore.exe <PATH>/src/scripts/**<script>** -i <ckt\_file> <options>, где:

<*PATH*> – домашняя директория САПР X-CAD,

<script> — управляющий скрипт на языке Tcl, обеспечивающий запуск главного исполняемого модуля, согласование входных и вывод выходных данных,

<ckt\_file> - полное имя файла с описанием проектируемой схемы,

<options> - опции запуска программы.

Каждая ПЛИС имеет свой управляющий скрипт, адаптированный под ее архитектуру и схемотехнические особенности. Соответствие названия ПЛИС и управляющего скрипта приведено ниже:

#### **5400TC015** – xa3

# Основные опции запуска программы:

| -h                                       | вывод на экран краткой справки о программе X-CAD    |  |

|------------------------------------------|-----------------------------------------------------|--|

| -i <ckt_file></ckt_file>                 | имя входного проектного файла формата Verilog или   |  |

|                                          | Tcl                                                 |  |

| -o <out_name></out_name>                 | задание имен выходных файлов                        |  |

| -top <top_name></top_name>               | определение имени модуля верхнего уровня. Задается  |  |

|                                          | в случае различия имени входного проектного файла и |  |

|                                          | модуля верхнего уровня.                             |  |

| Управление процессом логического синтеза |                                                     |  |

| -rtl                                     | синтез с помощью программы Cadence RTL Compiler     |  |

| -gen                                     | синтез с помощью программы Cadence Genus            |  |

| -dc                       | синтез с помощью программы Synopsys Design                        |

|---------------------------|-------------------------------------------------------------------|

|                           | Compiler                                                          |

| -y++                      | синтез с помощью программы Yosys                                  |

| Управл                    | ение процессом компоновки и размещения                            |

| -p <file></file>          | загрузка размещения элементов проектной схемы из                  |

|                           | заданного файла; если размещение содержится вместе                |

|                           | с нетлистом в Tcl-файле <ckt_file>, следует указать –р</ckt_file> |

|                           | "" (пустые кавычки)                                               |

| -inout <file></file>      | загрузка размещения ячеек ввода-вывода (ЯВВ) из                   |

|                           | заданного файла                                                   |

| -macro <file></file>      | загрузка размещения макроячеек из заданного файла                 |

| -ip_place <file></file>   | загрузка размещения IP блоков из заданного файла                  |

| -le <file></file>         | загрузка готовой планировки логических элементов из               |

|                           | заданного файла                                                   |

| -le_union <value></value> | Управление компоновкой логических элементов:                      |

|                           | 0 - выключение парной компоновки ЛЭ (компоновка                   |

|                           | только по сигналу SET/RESET);                                     |

|                           | 1 - компоновка ЛЭ по входам {a   d};                              |

|                           | 2 - компоновка по всем логическим входам ЛЭ;                      |

|                           | 3 - максимальный уровень компоновки, в том числе                  |

|                           | не связанных друг с другом ЛЭ.                                    |

| -sa_lm <value></value>    | задание множителя внутреннего цикла алгоритма                     |

|                           | размещения элементов;                                             |

|                           | увеличение значения параметра, увеличивает                        |

|                           | длительность и качество автоматического размещения;               |

|                                  | <value> - целое число из интервала [11000]</value>            |  |  |

|----------------------------------|---------------------------------------------------------------|--|--|

| Управление процессом трассировки |                                                               |  |  |

| -order <file></file>             | задание пользовательского порядка трассировки цепо            |  |  |

|                                  | проектной схемы, см. описание Tcl команды                     |  |  |

|                                  | xc_net_order                                                  |  |  |

| -sr <value></value>              | $-\mathbf{sr}$ — задание метода перетрассировки перегруженных |  |  |

| -rr <value></value>              | цепей в процессе автоматической трассировки,                  |  |  |

|                                  | $<$ value $>$ принимает одно из трех значений $\{0, 1, 2\}$ . |  |  |

|                                  | <b>-rr</b> – задание метода обхода трассировочных ресурсов    |  |  |

|                                  | ПЛИС,                                                         |  |  |

|                                  | <value> принимает одно из двух значений {0, 1}.</value>       |  |  |

|                                  | Возможные комбинации значений опций:                          |  |  |

|                                  | -sr 2 -rr 1 – по умолчанию: достигается оптимальный           |  |  |

|                                  | результат по времени и качеству трассировки;                  |  |  |

|                                  | -sr 2 -rr 0 — оптимизация времени трассировки;                |  |  |

|                                  | -sr 0 -rr 1 — оптимизация объема трассировочных               |  |  |

|                                  | ресурсов, используемых для имплементации                      |  |  |

|                                  | проектной схемы;                                              |  |  |

|                                  | -sr $0$ -rr $0$ – отсутствие оптимизации; может быть          |  |  |

|                                  | использована в случае, когда проектная схема не               |  |  |

|                                  | разводится при иных значениях                                 |  |  |

| -v_h <value></value>             | коэффициент учета истории перегруженности                     |  |  |

|                                  | коммутационного ресурса при трассировке,                      |  |  |

|                                  | <value> - любое число из интервала [01]</value>               |  |  |

| -v_p <value></value>     | коэффициент, отвечающий за влияние накопленного и                     |

|--------------------------|-----------------------------------------------------------------------|

|                          | собственного базового веса вершины графа                              |

|                          | трассировки,                                                          |

|                          | <value> - любое число из интервала [01]</value>                       |

| -path_w <value></value>  | ограничение суммарной накопленной стоимости                           |

|                          | прохождения сигнала для межсоединений,                                |

|                          | <value> - любое число из интервала [0500]</value>                     |

| -path_l <value></value>  | ограничение максимальной длины межсоединения, т.е.                    |

|                          | количества пройденных трассировочных элементов,                       |

|                          | <value> - целое число из интервала [1300]</value>                     |

| -ro_fast <value></value> | подключение предустановленных значений                                |

|                          | параметров трассировки для получения                                  |

|                          | трассировочного решения за кратчайшее время,                          |

|                          | <value> принимает одно из двух значений {0, 1}:</value>               |

|                          | -ro_fast 1 - значение "включено" по умолчанию.                        |

|                          | При включении опции заданные вручную значения                         |

|                          | параметров -sr, -rr, -v_h, -v_p, -path_w, -path_l                     |

|                          | игнорируются.                                                         |

|                          | <b>Внимание</b> ! Опция <b>не</b> может быть включена вместе с        |

|                          | опцией -ro_hq.                                                        |

| -ro_hq <value></value>   | подключение предустановленных значений                                |

|                          | параметров трассировки для достижения наилучшего                      |

|                          | качества трассировочного решения,                                     |

|                          | <value> принимает одно из двух значений {0, 1}:</value>               |

|                          | $-\mathbf{ro}_{\mathbf{hq}} \ 0$ - значение "выключено" по умолчанию. |

|                          |                                                                       |

|                | При включении опции заданные вручную значения       |  |  |

|----------------|-----------------------------------------------------|--|--|

|                | параметров -sr, -rr, -v_h, -v_p, -path_w, -path_l   |  |  |

|                | игнорируются.                                       |  |  |

|                | Внимание! Опция не может быть включена вместе с     |  |  |

|                | опцией -ro_fast.                                    |  |  |

| Управление про | щессом трассировки: поддержка устаревших опций      |  |  |

| -reroute       | выбор алгоритма трассировки:                        |  |  |

|                | 0 – алгоритм А* без разрыва и перетрассировки       |  |  |

|                | неразведенных цепей;                                |  |  |

|                | 1, 2 – алгоритм А* с двумя версиями метода разрыва  |  |  |

|                | и перетрассировки;                                  |  |  |

|                | 3 – алгоритм PathFinder (включен по умолчанию)      |  |  |

| -ripup         | ограничение на количество разрывов и                |  |  |

|                | перетрассировок для каждой цепи (учитывается при -  |  |  |

|                | reroute {1,2})                                      |  |  |

| -ro_iter       | ограничение на суммарное количество разрывов и      |  |  |

|                | перетрассировок всего списка цепей (учитывается при |  |  |

|                | -reroute {1,2})                                     |  |  |

## ВХОДНЫЕ ДАННЫЕ ПРОГРАММЫ

Входными данными для программы может быть описание схемы на разных уровнях представления данных. Так, если **<ckt\_name>** — название проектируемой схемы, то:

- 1. **<ckt\_name>.v** HDL описание схемы на языке Verilog требует обязательного запуска RTL-compiler, Genus, Design Compiler или Yosys.

- 2. **<ckt\_name>.sv** HDL описание схемы на языке System Verilog требует обязательного запуска RTL-compiler, Genus, Design Compiler или Yosys.

- 3. **<ckt\_name>.vhd** HDL описание схемы на языке VHDL требует обязательного запуска RTL-compiler, Genus, Design Compiler или Yosys.

- 4. <ckt\_name>.syn\_\*.v синтезированное Verilog описание схемы с использованием библиотечных и периферийных элементов ПЛИС. Файл может быть создан вручную или получен в результате синтеза с помощью RTL-compiler, Genus, Design Compiler, Yosys.

- 5. **<ckt\_name>.xmap.tcl** описание схемы на языке Tcl с использованием библиотечных элементов ПЛИС (является также одним из выходных файлов работы программы при использовании HDL описания в качестве исходного), как правило, требует наличия файла **<ckt\_name>.xmap.lib.tcl**.

```

Пример: c17.xmap.tcl, фрагмент

#INPUT LIST

set xc_input { N1 N2 N3 N6 N7 }

#OUTPUT LIST

set xc_output { N22 N23 }

#INPUT IOS

xc_inst {XC_BUF_N1} ibuf {a=N1 x=XC_I_N1} {inp_io=1}

xc_inst {XC_BUF_N2} ibuf {a=N2 x=XC_I_N2} {inp_io=1}

```

```

xc_inst {XC_BUF_N3} ibuf {a=N3 x=XC_I_N3} {inp_io=1}

xc_inst {XC_BUF_N6} ibuf {a=N6 x=XC_I_N6} {inp_io=1}

xc_inst {XC_BUF_N7} ibuf {a=N7 x=XC_I_N7} {inp_io=1}

#OUTPUT IOS

xc_inst {XC_BUF_N22} obuf {a=XC_O_N22 x=N22} {out_io=1}

xc_inst {XC_BUF_N23} obuf {a=XC_O_N23 x=N23} {out_io=1}

#LUTS

xc_inst {_1_} LE_cell_i3_11 { d=_0_c=XC_I_N3 b=XC_I_N1

y=XC_O_N22 }

xc_inst {_2_} LE_cell_i4_107 { d=XC_I_N7 c=XC_I_N2 b=XC_I_N6

a=XC_I_N3 y=XC_O_N23 }

xc_inst {_3_} LE_cell_i3_11 { d=XC_I_N2 c=XC_I_N6 b=XC_I_N3

y=_0_}

```

- 6. <ckt\_name>.inout.tcl файл размещения периферийных площадок ЯВВ. Подробное описание и примеры использования представлены в разделе «Использование файла размещения контактных площадок»

- 7. **<ckt\_name>.place.tcl** файл размещения логических элементов, содержащий команды на языке Tcl вида:

xc\_map\_inst <имя элемента> <имя посадочной площадки> Пример:

```

xc_map_inst cell_1 ILAB0101.ILE0701.ILE1

xc_map_inst cell_2 ILAB0101.ILE0801.ILE1

...

xc_map_inst cell_N ILAB0101.ILE1201.ILE2

```

8. **<ckt\_name>.le.tcl** — файл компоновки логических ячеек в логические элементы на языке Tcl вида:

```

xc_le <umя ЛЭ> {<umя ячейки> < umя ячейки>}

Пример:

xc_le LE_0 { cell_1 cell_3 }

xc_le LE_1 { cell_2 }

...

xc_le LE_N { cell_N }

```

#### БИБЛИОТЕКИ ЭЛЕМЕНТОВ ПЛИС

Библиотеки элементов ПЛИС расположены в соответствующих поддиректориях **X-CAD/src/libraries/<chip>/<lib\_case>**, где **<chip>** определяется в соответствии с таблицей:

## **5400TC015** – XA3

case> – один из доступных углов характеризации:

- PwcV1.65T125 худший случай (напряжение 1.65В, температура 125°С)

- **PtcV1.80T25** стандартный (напряжение 1.8B, температура 25°C)

- **PbcV1.95Tm40** лучший случай (напряжение 1.95B, температура 40°С)

Библиотеки представлены в следующих форматах:

- \*.tcl описание конфигурирования элементов ПЛИС.

- \*.lib библиотека элементов в стандарте Liberty.

- \*.v библиотека элементов в формате Verilog.

Специальные обозначения используемые в названиях библиотек:

- LE библиотека логических элементов ПЛИС.

- **IO** библиотека элементов ввода-вывода ПЛИС.

- **RE** библиотека коммутационных элементов ПЛИС.

## ИСПОЛЬЗОВАНИЕ КОНТАКТНЫХ ПЛОЩАДОК

Автоматизация представленного маршрута проектирования подразумевает автоматическую генерацию экземпляров модулей ячеек ввода-вывода на основании списков имен входных и выходных портов Verilog-описания схемы.

Уникальное *имя*, присваиваемое *экземпляру ячейки*, имеет вид:

$$XC\_BUF\_<$$

имя порта $>$

У входной ячейки имя внутреннего сигнала, входящего в ПЛИС, принимает вид:

$$\mathit{XC}\_\mathit{I}\_<\!\mathit{им}\mathit{я}$$

порта $>$

У выходной ячейки имя внутреннего сигнала, приходящего из ПЛИС, принимает вид:

У входной и выходной ячеек, предназначенных для тактового сигнала, имя внутреннего сигнала принимает вид:

$$XC\_C\_<$$

имя порта $>$

Внешние сигналы ячеек ввода/вывода, связанные с периферией, сохраняют имя соответствующего им порта из Verilog-описания устройства.

**Пример** автоматически сгенерированных экземпляров модулей входной, выходной и тактовых ячеек:

Экземпляр модуля ячейки ввода/вывода может быть добавлен вручную в соответствии с тем стандартом языка аппаратуры, который поддерживается

используемым программным обеспечением для выполнения логического синтеза.

**Пример** добавленных вручную экземпляров модулей входной и выходной ячеек:

```

xa_ib u1 (.a(G0), .x(G0_int));

xa_ob u2 (.a(G17_int), .x(G17));

```

**Пример** добавленных вручную экземпляров модулей входной и выходной тактовых ячеек:

```

xa_clk_ib clk1 (.a(CK), .x(CK_int));

xa_clk_ob clk2 (.a(CK_int), .x(CK_out));

```

Использование выходной тактовой ячейки (как автоматически сгенерированной, так и добавленной пользователем) возможно только в том случае, когда выходной тактовый сигнал повторяет входной (когда выходному тактовому сигналу назначается входной).

Данная ситуация показана на следующем примере:

```

module clk_in_out(clk_in, clk_out, rst_n, data, out);

input clk_in, rst_n, data;

output clk_out, out;

wire clk_in_int, clk_out_int;

xa_clk_ib clk1 (.a(clk_in), .x(clk_in_int));

xa_clk_ob clk2 (.a(clk_out_int), .x(clk_out));

always @(posedge clk_in_int or negedge rst_n)

begin

if(~rst_n) begin

out <= 0;

end else begin</pre>

```

```

out <= data;

end

end

assign clk_out_int = clk_in_int;

endmodule</pre>

```

Также пользователю доступно использование специализированной контактной площадки PAD\_RST, позволяющей глобально осуществить сброс всех триггеров на кристалле ПЛИС.

Для назначения сигнала сброса на данную контактную площадку необходимо при разработке Verilog-описания задать этому сигналу имя «GRESET».

Пример использования контактной площадки глобального сброса:

```

module greset(clk_in, GRESET, data, out);

input clk_in, GRESET, data;

output out;

always @(posedge clk_in or posedge GRESET) begin

if(GRESET) begin

out <= 0;

end else begin

out <= data;

end

end</pre>

```

endmodule

# ФАЙЛ РАЗМЕЩЕНИЯ КОНТАКТНЫХ ПЛОЩАДОК

<ckt\_name>.inout.tcl — файл размещения периферийных площадок ПЛИС. Файл имеет следующий синтаксис описания:

```

set xc(inout) {

{<uмя порта > <uмя контактной площадки>}

...

{<uмя порта > <uмя контактной площадки>}

}

set xc(inout_type) {

{<uмя порта > <mun площадки > <nuн площадки>}

...

{<uмя порта > <mun площадки > <nuн площадки>}

...

{<uмя порта > <mun площадки > <nuн площадки>}

},

```

где  $< uмя \ nopma>$  - имя входного/выходного порта RTL описания схемы;  $< uмя \ контактной \ площадки>$  площадки> - имя контактной площадки ПЛИС, на которой размещен порт,  $< mun \ nnow adku>$  - тип контактной площадки / имя библиотечного элемента контактной площадки;  $< nuh \ nnow adku>$  - пин контактной площадки, к которому подключен пор

Входные/выходные порты RTL описания схемы, отсутствующие в файле <ckt\_name>.inout.tcl, будут размещены на контактные площадки автоматически.

**Пример** Verilog-описания и соответствующего ему файла размещения контактных площадок:

```

module fa ( input a, b, c, output sum, carry );

```

```

wire d,e,f;

wire a_in;

xa_ib m0 (.a(a), .x(a_in));

xor(sum,a_in,b,c);

and(d,a_in,b);

and(e,b,c);

and(f,a_in,c);

or(carry,d,e,f);

endmodule

```

m0 — пример определенного вручную экземпляра ячейки ввода/вывода. Экземпляры ячеек для сигналов b, c, carry будут добавлены автоматически. Площадка для сигналов a и sum назначаются в соответствии c inout-файлом. Площадки для b, c, carry будут назначены автоматически.

```

set xc(inout) {

{ a FROM_PAD1}

{ sum TO_PAD205}

}

set xc(inout_type) {

{ a xa_ib a}

{ sum xa_ob x}

}

```

Файл **<ckt\_name>.inout.tcl** может быть получен при помощи интерфейса планировки кристалла FloorPlanner. Подробное описание работы с данной

программой представлено в разделе <u>ИНТЕРФЕЙС ПЛАНИРОВКИ</u> <u>КРИСТАЛЛА FLOORPLANNER</u>.

Файл с размещением периферийных площадок должен быть подключен к проекту с помощью опции -*inout* в консольном или в графическом режиме.

# ИСПОЛЬЗОВАНИЕ ИМЕН КОНТАКТНЫХ ПЛОЩАДОК

Автоматическую генерацию и размещение ЯВВ можно выполнить, используя в Verilog-описании схемы названия портов, совпадающие с именем контактной площадки. Имена контактных площадок заданы в соответствии с их назначением и именами внешних портов ПЛИС. Доступные контактные площадки представлены в таблицах ниже.

| Название  | Имя контактной | Специализированное имя | Тип        |

|-----------|----------------|------------------------|------------|

| кристалла | площадки       | контактной площадки    | контактной |

|           |                |                        | площадки   |

|           |                |                        |            |

| 5400TC015 | IO[190:0]      |                        | xa_ib,     |

|           |                |                        | xa_ob      |

#### ВЫПОЛНЕНИЕ СТАТИЧЕСКОГО ВРЕМЕННОГО АНАЛИЗА

Запуск выполнения статического временного анализа (СВА) проектируемой схемы производится в автоматическом режиме. Для установки тактовых сигналов, определения временных ограничений и изменения других настроек СВА следует использовать опции запуска.

## Основные опции запуска СВА:

| Управление процессом статического временного анализа |                                                                     |  |

|------------------------------------------------------|---------------------------------------------------------------------|--|

| -clk <list></list>                                   | – определение списка тактовых сигналов в проекте                    |  |

| -per <list></list>                                   | – определение значений периодов тактовых сигналов                   |  |

| -sta_rise <value></value>                            | – определение времени нарастания входного сигнала                   |  |

| -sta_fall <value></value>                            | – определение времени спада входного сигнала                        |  |

| -sta_tran <value></value>                            | <ul> <li>определение времени нарастания и спада входного</li> </ul> |  |

|                                                      | сигнала                                                             |  |

| -sta_max_delay                                       | – определение значения максимальной задержки на                     |  |

| <value></value>                                      | главных выходах схемы                                               |  |

| -sta_num_crit                                        | – определение количества критических путей,                         |  |

| <value></value>                                      | выведенных в отчет                                                  |  |

| -sta_sdc <file_path></file_path>                     | – определение полного пути до файла временными                      |  |

|                                                      | ограничениями проекта                                               |  |

Результаты CBA генерируются по завершению работы программы в папку <top\_name>.STA.reports.

Результатом проведенного CBA схемы до этапа трассировки является следующий набор файлов:

• <top\_name>.gate.nworst.txt — временной отчет для заданного количества наиболее медленных критических путей;

• <top\_name>.gate.sdf — файл с задержками и заданными временными ограничениями.

Результатом проведенного CBA схемы после этапа трассировки является следующий набор файлов:

- <top\_name>.routed.nworst. txt временной отчет для заданного количества наиболее медленных критических путей;

- <top\_name>.routed.sdf файл с задержками и заданными временными ограничениями.

# Доступные временные ограничения для использования в SDC файле:

| create_clock           | set_multicycle_path  |

|------------------------|----------------------|

| set_clock_latency      | set_input_transition |

| set_clock_uncertainty  | set_input_delay      |

| set_clock_transition   | set_output_delay     |

| set_propagated_clock   | set_max_delay        |

| create_generated_clock | set_min_delay        |

| set_false_path         | set_load             |

| set_disable_timing     | set_case_analysis    |

• **create\_clock** – добавить к анализу тактовый сигнал, его источник, период, время нарастания и спада сигнала.

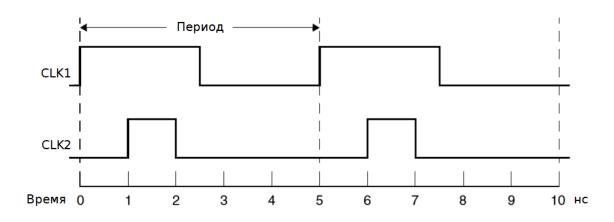

-waveform задать коэффициент заполнения тактового сигнала. По умолчанию, коэффициент заполнения <T rise> равен 50%, что эквивалентно <T rise> =<T fall> HC,  $\langle T \text{ fall} \rangle = (\langle T \text{ per} \rangle / 2) HC$ . <T rise> <T fall> время начала нарастания и начала спада сигнала. <source> источник создаваемого синхросигнала (порт, пин). По умолчанию тактовый сигнал будет назван по имени источника. При желании можно указать имя тактового с помощью опции -name..

Пример использования команды:

create\_clock -period 5 [get\_ports CLK1]

create\_clock -period 5 -waveform {1 2}[get\_ports CLK2]

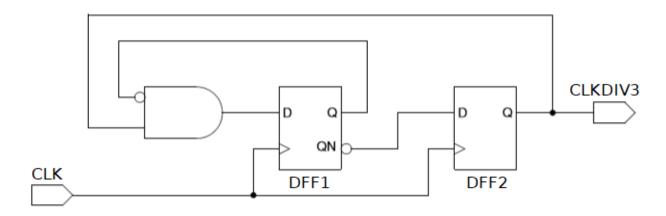

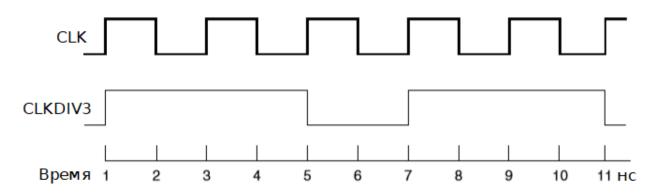

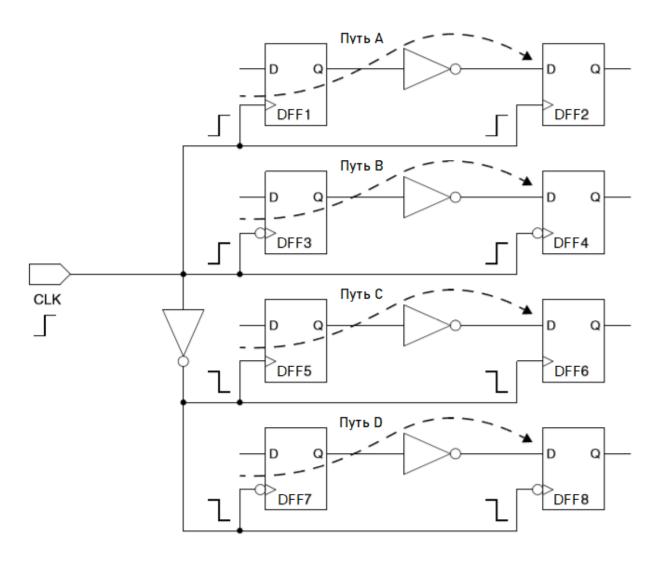

Результат определения коэффициента заполнения тактового сигнала по умолчанию и с использованием опции -waveform показан на рисунке 4.

Рисунок 4 – Диаграммы тактовых сигналов

• set\_clock\_latency – установить время задержки тактового сигнала.

set\_clock\_latency [-rise/-fall] [-min][-max] [-source]

[-late] [-early] <delay\_value> <name>,

| -rise                       | _ | задать задержку только при нарастании      |

|-----------------------------|---|--------------------------------------------|

|                             |   | тактового сигнала;                         |

| -fall                       | _ | задать задержку только при убывании        |

|                             |   | тактового сигнала;                         |

| -min                        | _ | задать только минимальную задержку         |

|                             |   | тактового сигнала;                         |

| -max                        | _ | задать только максимальную задержку        |

|                             |   | тактового сигнала;                         |

| -source                     | _ | задать только задержку задержка источника; |

| -late                       | _ | задать только позднее время прибытия от    |

|                             |   | источника;                                 |

| -early                      | _ | задать только раннее время прибытия от     |

|                             |   | источника;                                 |

| <delay_value></delay_value> | _ | значение времени задержки;                 |

| <name></name>               | _ | установить имя тактового сигнала, для      |

|                             |   | которого задается задержка.                |

Задержка clock latency состоит из двух:

- source latency—задержка источника—время, требуемое синхросигналу, для распространения от источника до точки указанной в проекте.

- network\_latency задержка сети время, требуемое синхросигналу,

чтобы дойти от точки, указанной в проекте, до тактового вывода

последовательностного элемента.

В данном случае задержкой источника является задержка ЯВВ, которая добавляется в проект автоматически. Её задержка определяется программой из характеризованной библиотеки.

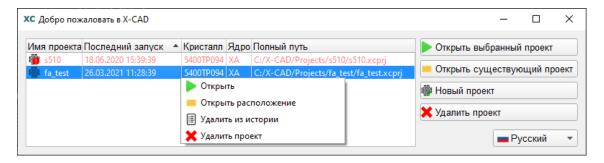

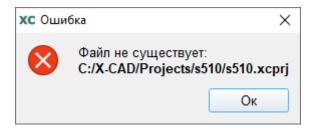

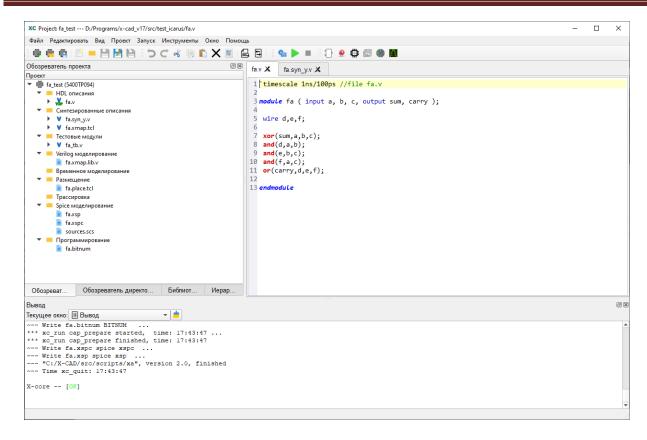

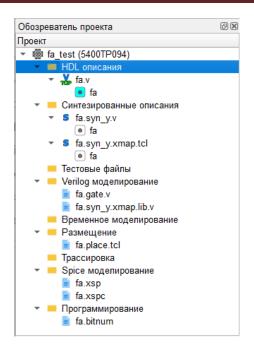

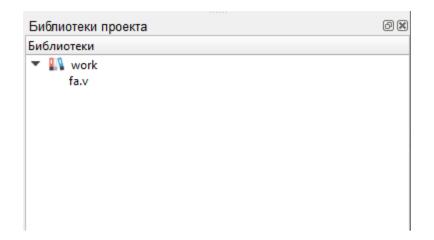

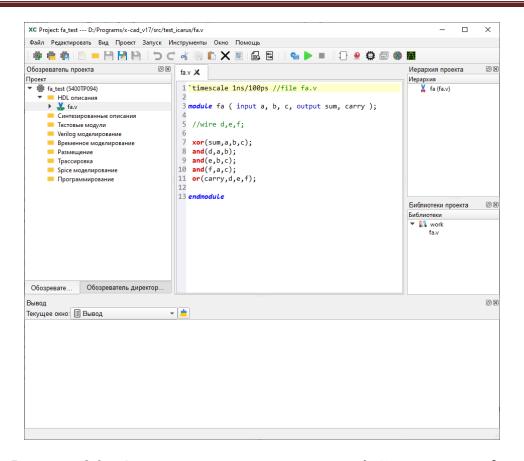

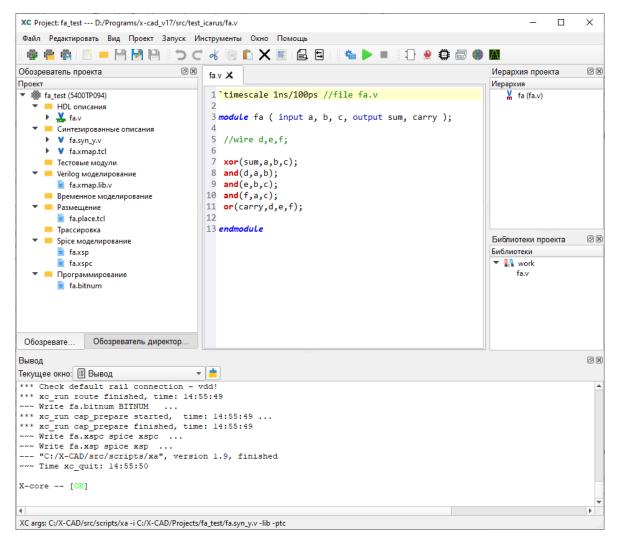

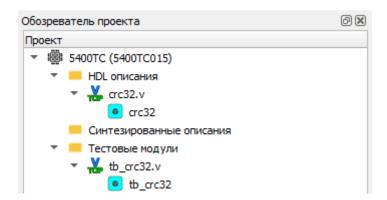

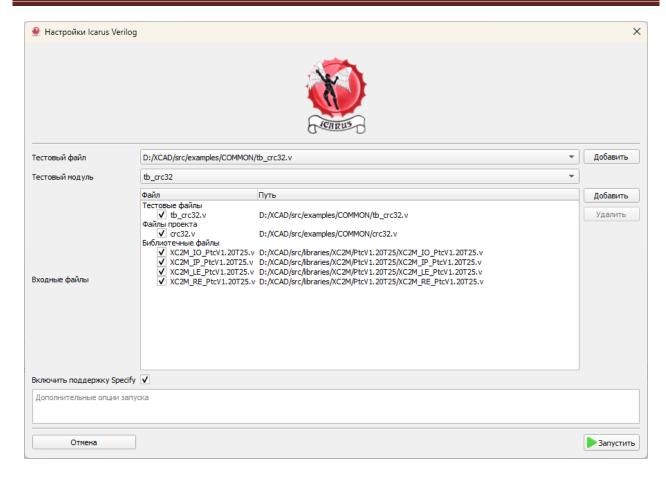

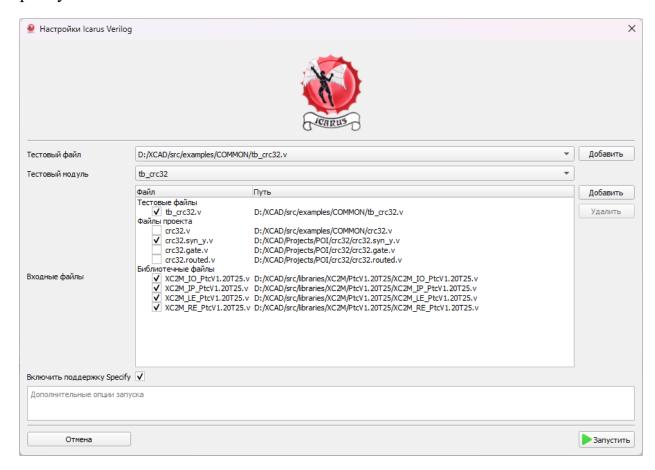

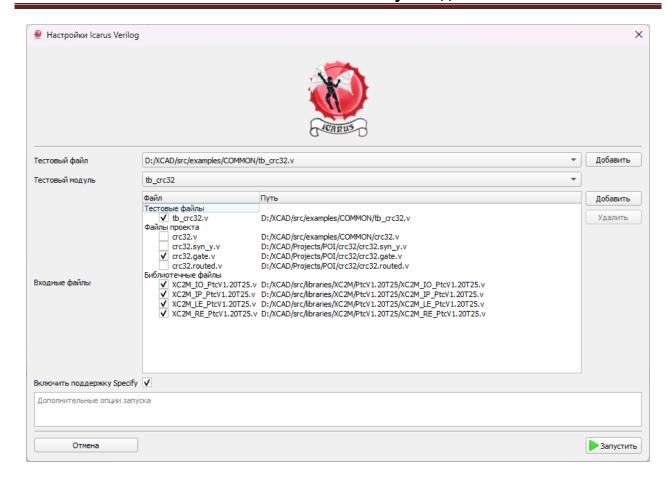

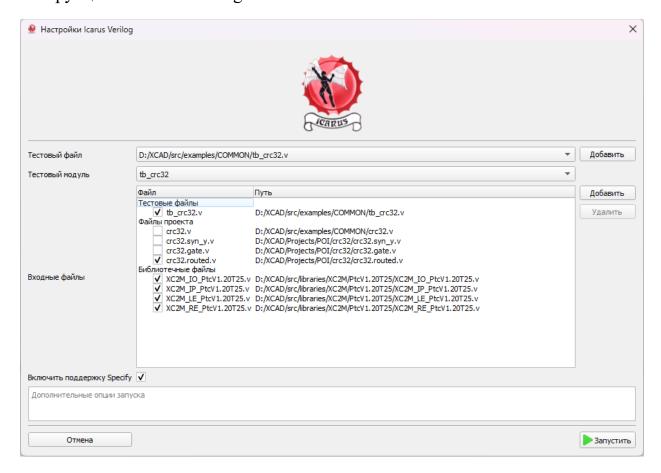

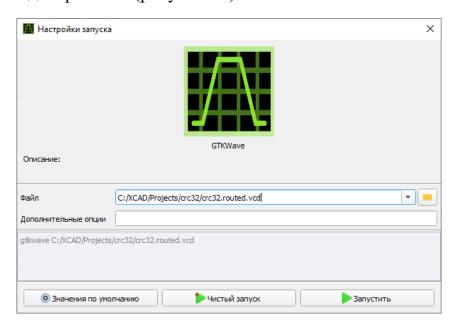

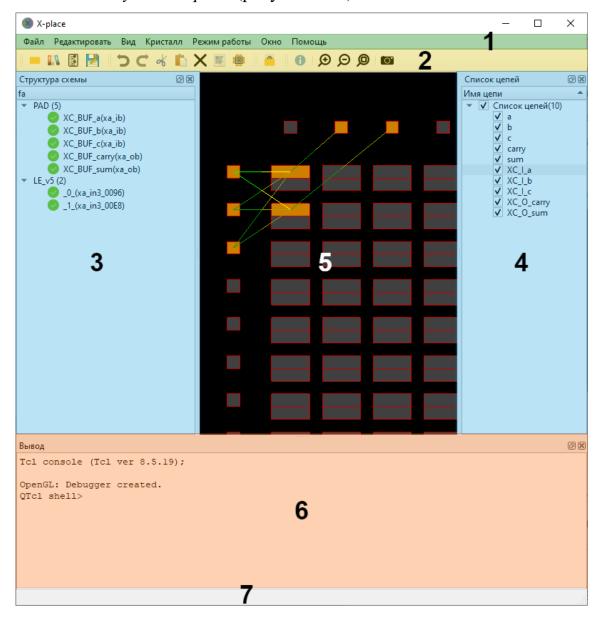

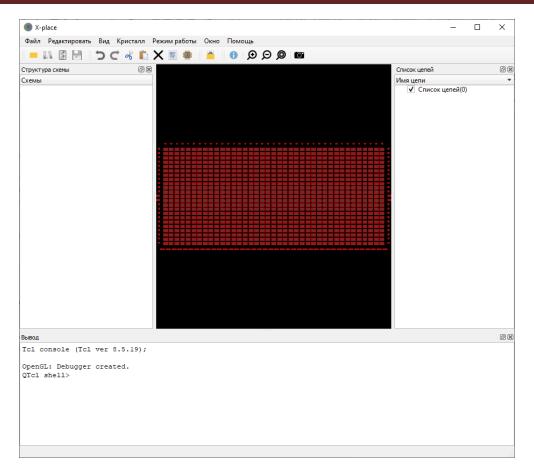

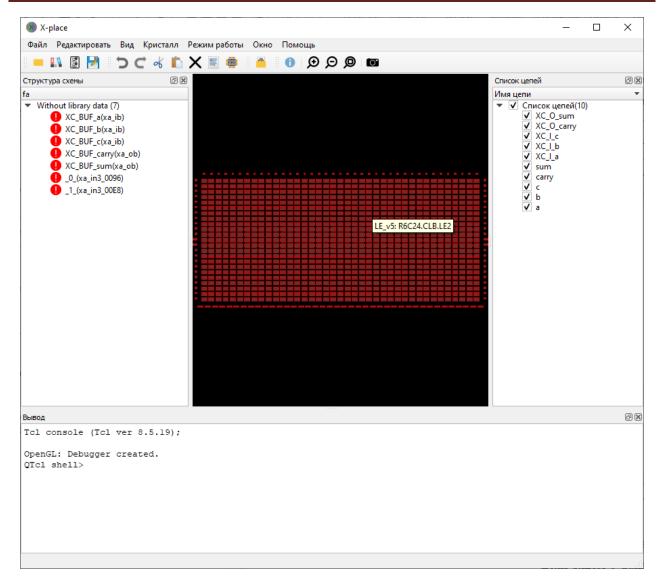

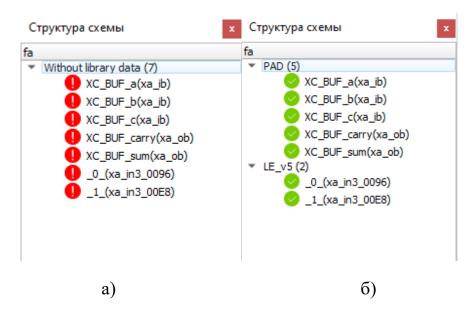

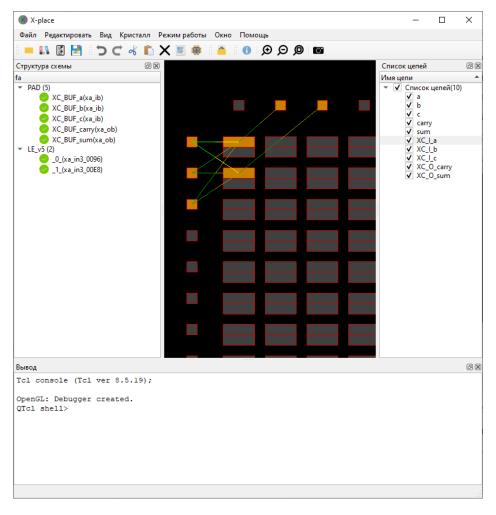

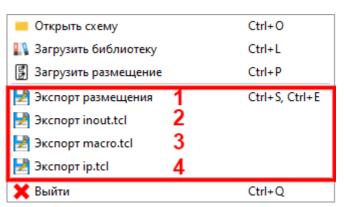

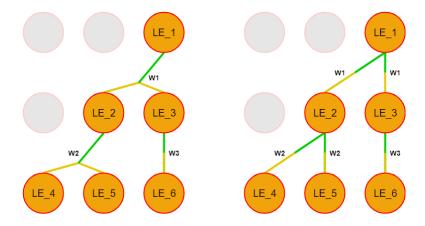

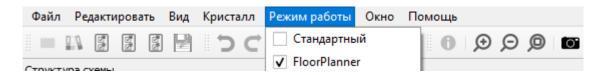

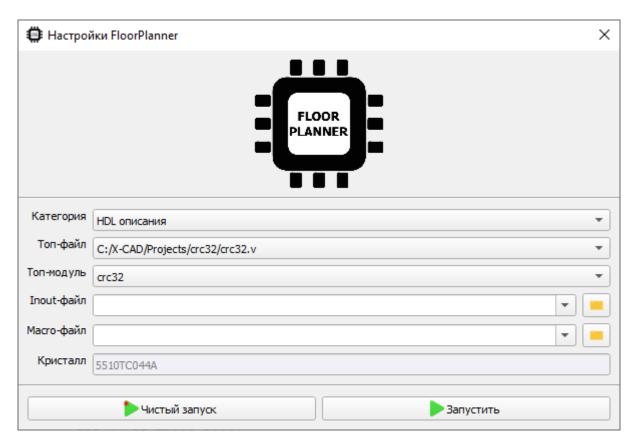

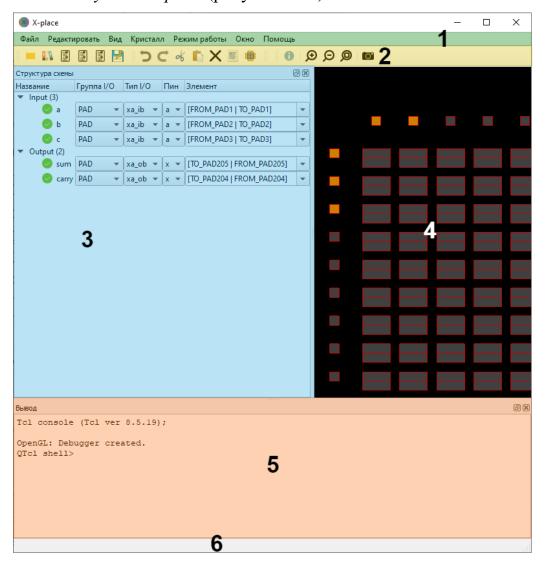

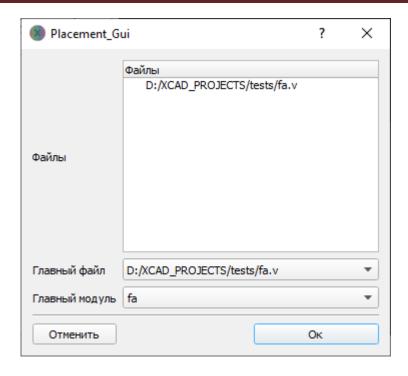

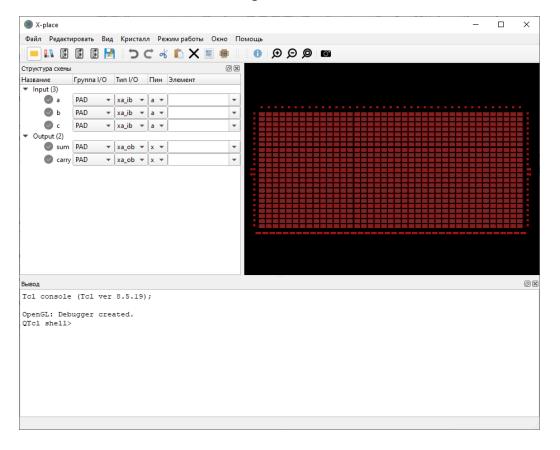

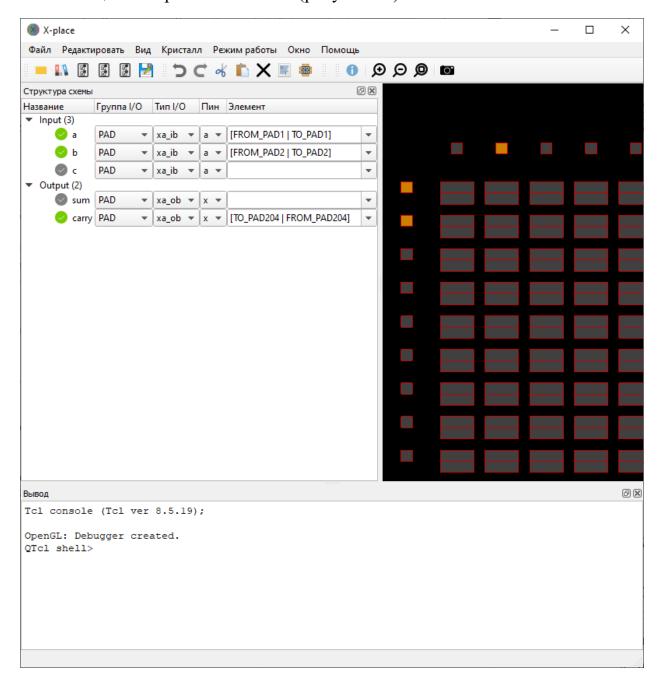

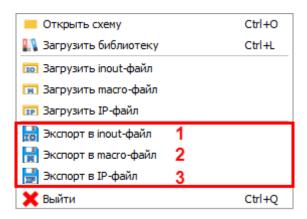

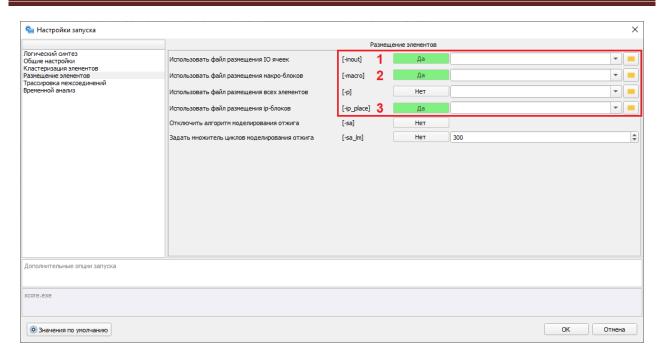

Задержка сети определяется программой за счет оценки реальных трассировочных элементов, используемых в схеме для коммутации