Микросхема преобразователя сигналов с датчиков перемещения в цифровой код угла

Версия 0.1 **5400ТР065А-022**

#### Основные особенности

- Диапазон напряжения питания от 3,3 В до 5,0 В;

- Период обновления информации не менее 1 мкс;

- Частота возбуждения датчиков от 0 до 30 кГц;

- Разрядность выходной информации от 8 бит до 16 бит;

- Два независимых преобразователя первичной;

- Два независимых генератора опорных сигналов с частотой от 20 Гц до 30 кГц;

- Эмуляция квадратурного энкодера;

- Последовательный (SPI) интерфейс;

- Температурный диапазон от –60°C до +125°C.

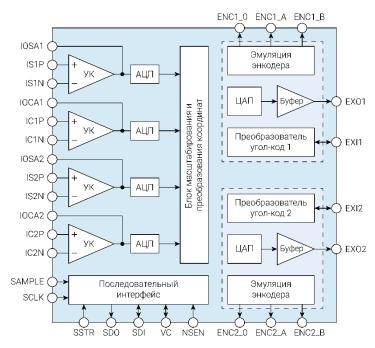

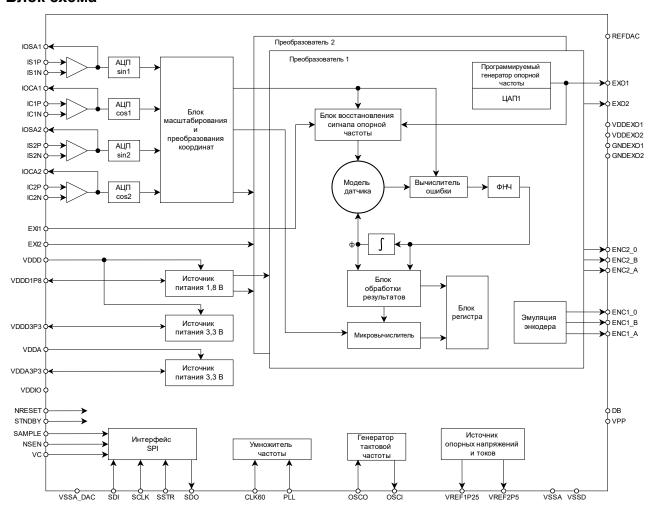

Рисунок 1. Структурная схема

### Общее описание

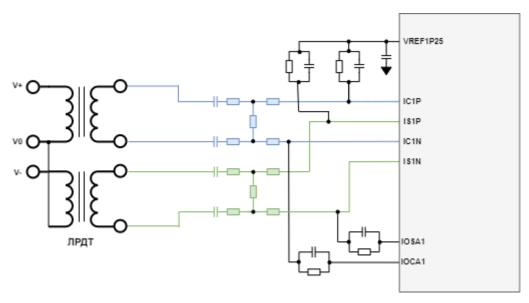

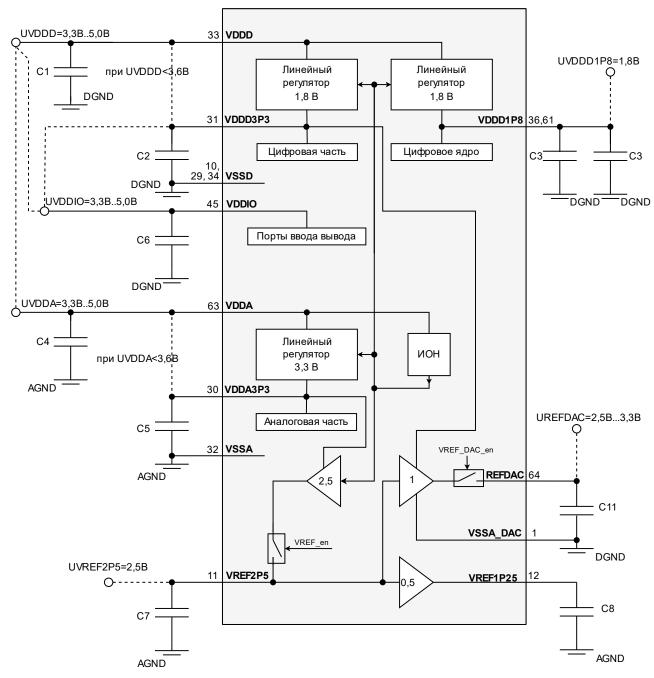

Микросхема предназначена для преобразования сигналов с датчиков типа сельсин, СКВТ (синусно-косинусный вращающийся трансформатор) и датчиков линейного перемещения — ЛРДТ (линейный регулируемый дифференциальный трансформатор). Микросхема в своем составе содержит программируемый генератор возбуждающего напряжения и два следящих контура, производящих вычисление угла поворота вала или перемещения сердечника ЛРДТ.

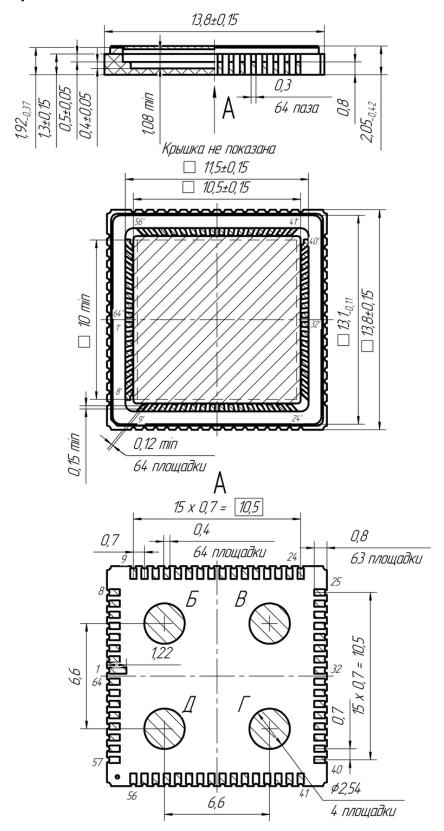

Микросхема выполнена в 64-х выводном металлокерамическом корпусе 5153.64-3.

Обращаем внимание, документация носит ознакомительный характер. При разработке аппаратуры необходимо руководствоваться КД: технические условия АЕНВ.431260.392ТУ, карта заказа КФЦС.431260.041-022Д16.

Версия 0.1

# Электрические параметры микросхемы

Таблица 1. Электрические характеристики (температурный диапазон от – 60°C до +125°C)

|                                                                                                       | Норма параметра |         |          |  |  |

|-------------------------------------------------------------------------------------------------------|-----------------|---------|----------|--|--|

| Параметр, единица измерения                                                                           | не менее        | типовое | не более |  |  |

| Выходное напряжение ИОН для формирования опорного напряжения АЦП, В                                   | 2,375           |         | 2,625    |  |  |

| Ток потребления в режиме покоя, мА                                                                    |                 |         |          |  |  |

| STNDBY = «0»                                                                                          |                 |         | 15       |  |  |

| STNDBY = «1»                                                                                          |                 |         | 12       |  |  |

| Динамический ток потребления, мА при SHDN = «0»                                                       |                 |         | 200      |  |  |

| Динамический ток потребления, мА<br>при SHDN = «1»                                                    |                 |         | 100      |  |  |

| Входной ток, мА<br>на выводах VREF2P5, в режиме подключения<br>внешнего источника опорного напряжения |                 |         | 10       |  |  |

| Выходное напряжение высокого уровня, В                                                                |                 | 2,4     | VDDIO    |  |  |

| Выходное напряжение низкого уровня, В                                                                 | 0               | 0,4     |          |  |  |

| Минимальное напряжение<br>(EXO1, EXO2), В                                                             |                 |         | 0,4      |  |  |

| Максимальное напряжение<br>(EXO1, EXO2), В                                                            | VDDEXO –<br>0,4 |         |          |  |  |

| Частота выходного сигнала, кГц,<br>(сигнала опорной частоты) основная гармоника                       | 0,02            |         | 30       |  |  |

# Электростатическая защита

Микросхема имеет встроенную защиту от электростатического разряда до 1000 В по модели человеческого тела. Требует мер предосторожности.

Обращаем внимание, документация носит ознакомительный характер. При разработке аппаратуры необходимо руководствоваться КД: технические условия АЕНВ.431260.392ТУ, карта заказа КФЦС.431260.041-022Д16.

# Предельно-допустимые и предельные режимы эксплуатации

Таблица 2. Предельно-допустимые и предельные режимы эксплуатации микросхем

| Параметр, единица измерения                               | -        | ельно-<br>ый режим   | Предельный режим |          |

|-----------------------------------------------------------|----------|----------------------|------------------|----------|

|                                                           | не менее | не более             | не менее         | не более |

| Напряжение питания аналоговой части<br>(VDDA), B          | 3,0      | 5,25                 | - 0,3            | 5,5      |

| Напряжение питания цифровой части (VDDD), В               | 3,0      | 5,25                 | - 0,3            | 5,5      |

| Напряжение питания интерфейсной части<br>(VDDIO), В       | 3,0      | 5,25                 | - 0,3            | 5,5      |

| Входное опорное напряжение<br>АЦП (VREF2P5), В            | 2,45     | 2,55                 | 0                | 5,5      |

| Входное напряжение высокого уровня<br>цифровых выводов, В | 2,0      | VDDIO <sup>(1)</sup> | - 0,3            | 5,5      |

| Входное напряжение низкого уровня цифровых выводов, В     | 0        | 0,8                  | - 0,3            | 5,5      |

| Температура эксплуатации, °С                              | -60      | +125                 | -60              | +150     |

| Примечание:                                               | •        |                      |                  |          |

<sup>1)</sup> Не более 5,25 В

Обращаем внимание, документация носит ознакомительный характер. При разработке аппаратуры необходимо руководствоваться КД: технические условия АЕНВ.431260.392ТУ, карта заказа КФЦС.431260.041-022Д16.

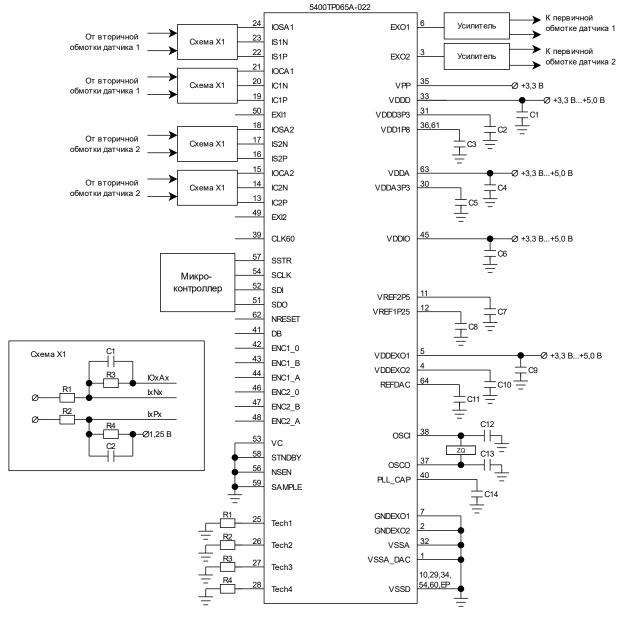

# Конфигурация и функциональное описание выводов

Таблица 3. Функциональное назначение выводов микросхемы

| 1         VSSA_DAC         РWR         Общий вывод опорного напряжения ЦАП генератора опорной частоты           2         GNDEXO2         PWR         Общий вывод генератора опорной частоты 2           3         EXO2         AO         Выход генератора опорной частоты 2           4         VDDEXO1         PWR         Питание генератора опорной частоты 1           6         EXO1         AO         Выход генератора опорной частоты 1           7         GNDEXO1         PWR         Общий вывод пенератора опорной частоты 1           8, 9         NC         —         Не используется           10, 29, 344, 54, VSSD         PWR         Общий вывод питания цифровой части           60         VREF1P25         AI/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           11         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соs2           14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя соз2           16         IS2P         AI         Прямой вход усилителя віл2           17         IS2N         AI         Ин                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Nº      | Наименование | Тип    | Назначение вывода                                                                              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|--------|------------------------------------------------------------------------------------------------|--|

| 1         VSSA_DAC         PWR         опорной частоты           2         GNDEXO2         PWR         Общий вывод генератора опорной частоты 2           3         EXO2         AO         Выход генератора опорной частоты 2           4         VDDEXO1         PWR         Питание генератора опорной частоты 1           6         EXO1         AO         Выход генератора опорной частоты 1           7         GNDEXO1         PWR         Общий вывод питания цифровой части           8, 9         NC         — Не используется           10, 29, 34, 54, VSSD         PWR         Общий вывод питания цифровой части           60         VREF2P5         AI/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           11         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой окод усилителя соs2           14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя sin2           16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя sin2           18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | вывода  | вывода       | вывода |                                                                                                |  |

| 3   EXO2   AO   Выход генератора опорной частоты 2   4   VDDEXO1   PWR   Питание генератора опорной частоты 1   5   VDDEXO1   PWR   Питание генератора опорной частоты 1   6   EXO1   AO   Выход генератора опорной частоты 1   7   GNDEXO1   PWR   Общий вывод генератора опорной частоты 1   8, 9   NC   — Не используется   10, 29, 34, 54,   VSSD   PWR   Общий вывод питания цифровой части   11   VREF2P5   AI/AO   Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)   12   VREF1P25   AO   Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)   13   IC2P   AI   Прямой вход усилителя соs2   14   IC2N   AI   Прямой вход усилителя соs2   15   IOCA2   AO   Выход буферного усилителя соs2 (вход АЦП соs2)   16   IS2P   AI   Прямой вход усилителя sin2   17   IS2N   AI   Инверсный вход усилителя sin2   18   IOSA2   AO   Выход буферного усилителя sin2   19   IC1P   AI   Прямой вход усилителя соs1   20   IC1N   AI   Инверсный вход усилителя соs1   21   IOCA1   AO   Выход буферного усилителя соs1 (вход АЦП соs1)   22   IS1P   AI   Прямой вход усилителя sin1   23   IS1N   AI   Инверсный вход усилителя sin1 (вход АЦП соs1)   24   IOSA1   AO   Выход буферного усилителя sin1 (вход АЦП sin1)   25   Тесh1   — Технологический вывод   26   Тесh2   — Технологический вывод   27   Тесh3   — Технологический вывод   28   Тесh4   — Технологический вывод   29   Тесh3   — Технологический вывод   30   VDDA3P3   PWR   Выход линейного регулятора напряжения питания анапоговой части (шунтируется конденсатором)   31   VDDD3P3   PWR   Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)   32   VSSA   PWR   Общий вывод питания анапоговой части (шунтируется конденсатором)   33   VDDD   PWR   Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором) | 1       | VSSA_DAC     | PWR    |                                                                                                |  |

| 4         VDDEXO2         PWR         Питание генератора опорной частоты 2           5         VDDEXO1         PWR         Питание генератора опорной частоты 1           6         EXO1         AO         Выход генератора опорной частоты 1           7         GNDEXO1         PWR         Общий вывод генератора опорной частоты 1           8,9         NC         — Не используется           10, 29, 34, 54, 60         VSSD         PWR         Общий вывод питания цифровой части           60         WREF1P25         AI/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           11         VREF1P25         AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           12         VREF1P25         AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соз2           14         IC2N         AI         Прямой вход усилителя соз2           15         IOCA2         AO         Выход буферного усилителя соз2           16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя sin2 (вход АЦП sin2)           19         IC1P         AI </td <td>2</td> <td>GNDEXO2</td> <td>PWR</td> <td>Общий вывод генератора опорной частоты 2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2       | GNDEXO2      | PWR    | Общий вывод генератора опорной частоты 2                                                       |  |

| 5         VDDEXO1         PWR         Питание генератора опорной частоты 1           6         EXO1         AO         Выход генератора опорной частоты 1           7         GNDEXO1         PWR         Общий вывод генератора опорной частоты 1           8, 9         NC         — Не используется           10, 29, 34, 54, 60         VSSD         PWR         Общий вывод питания цифровой части           11         VREF1P25         AI/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           12         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соs2           14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя соs2 (вход АЦП соs2)           16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя cos1           18         IOSA2         AO         Выход буферного усилителя cos1           21         IOCA1         AO         Выход буферного усилителя cos1           22         IS1P         AI         Прямой вход усилителя sin1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3       | EXO2         | AO     | Выход генератора опорной частоты 2                                                             |  |

| 6         EXO1         AO         Выход генератора опорной частоты 1           7         GNDEXC1         PWR         Общий вывод генератора опорной частоты 1           8, 9         NC         — Не используется           10, 29, 34, 54, 60         VSSD         PWR         Общий вывод питания цифровой части           11         VREF2P5         AI/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           12         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соѕ2           14         IC2N         AI         Инверсный вход усилителя соѕ2           15         IOCA2         AO         Выход буферного усилителя соѕ2           16         IS2P         AI         Инверсный вход усилителя соѕ2           17         IS2N         AI         Инверсный вход усилителя соѕ1           18         IOSA2         AO         Выход буферного усилителя соѕ1           20         IC1N         AI         Инверсный вход усилителя соѕ1           21         IOCA1         AO         Выход буферного усилителя соѕ1 (вход АЦП соѕ1)           22         IS1P         AI         Прямой вход усилителя соѕ1 (вход АЦП соѕ1) </td <td>4</td> <td>VDDEXO2</td> <td>PWR</td> <td>Питание генератора опорной частоты 2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4       | VDDEXO2      | PWR    | Питание генератора опорной частоты 2                                                           |  |

| 7         GNDEXO1         PWR         Общий вывод генератора опорной частоты 1           8, 9         NC         — Не используется           10, 29, 34, 54, 60         VSSD         PWR         Общий вывод питания цифровой части           11         VREF2P5         Al/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           12         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соs2           14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя соs2           16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя sin2 (вход АЦП sin2)           19         IC1P         AI         Прямой вход усилителя cos1           20         IC1N         AI         Инверсный вход усилителя cos1           21         IOCA1         AO         Выход буферного усилителя sin1           22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5       | VDDEXO1      | PWR    | Питание генератора опорной частоты 1                                                           |  |

| 8, 9         NC         —         Не используется           10, 29, 34, 54, 60         VSSD         PWR         Общий вывод питания цифровой части           11         VREF2P5         AI/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           12         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соs2           14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя соs2 (вход АЦП соs2)           16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя sin2           18         IOSA2         AO         Выход буферного усилителя соs1           19         IC1P         AI         Прямой вход усилителя соs1           20         IC1N         AI         Инверсный вход усилителя соs1           21         IOCA1         AO         Выход буферного усилителя sin1           22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6       | EXO1         | AO     | Выход генератора опорной частоты 1                                                             |  |

| 10, 29, 34, 54, 60         VSSD         PWR         Общий вывод питания цифровой части           11         VREF2P5         Al/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           12         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соs2           14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя соs2           16         IS2P         AI         Инверсный вход усилителя sin2           18         IOSA2         AO         Выход буферного усилителя sin2           18         IOSA2         AO         Выход буферного усилителя sin2           19         IC1P         AI         Прямой вход усилителя cos1           20         IC1N         AI         Инверсный вход усилителя cos1           21         IOCA1         AO         Выход буферного усилителя sin1           22         IS1P         AI         Прямой вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1           25         Tech1         —         Технологический вывод                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7       | GNDEXO1      | PWR    | Общий вывод генератора опорной частоты 1                                                       |  |

| 34, 54, 60         VSSD         PWR         Общий вывод питания цифровой части           11         VREF2P5         AI/AO         Вывод источника опорного напряжения АЦП 2,5 В (шунтируется конденсатором)           12         VREF1P25         AO         Вывод источника опорного напряжения 1,25 В. (шунтируется конденсатором)           13         IC2P         AI         Прямой вход усилителя соs2           14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя соs2           16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя sin2           18         IOSA2         AO         Выход буферного усилителя sin2 (вход АЦП sin2)           19         IC1P         AI         Инверсный вход усилителя cos1           21         IOCA1         AO         Выход буферного усилителя sin1           22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Tech1         —         Технологический вывод                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8, 9    | NC           | _      | Не используется                                                                                |  |

| VREF2PS   AI/AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34, 54, | VSSD         | PWR    | Общий вывод питания цифровой части                                                             |  |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11      | VREF2P5      | AI/AO  | 1                                                                                              |  |

| 14         IC2N         AI         Инверсный вход усилителя соs2           15         IOCA2         AO         Выход буферного усилителя соs2 (вход АЦП соs2)           16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя sin2           18         IOSA2         AO         Выход буферного усилителя sin2 (вход АЦП sin2)           19         IC1P         AI         Прямой вход усилителя cos1           20         IC1N         AI         Инверсный вход усилителя cos1           21         IOCA1         AO         Выход буферного усилителя sin1           22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Теch1         —         Технологический вывод           26         Тесь2         —         Технологический вывод           27         Тесh3         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12      | VREF1P25     | AO     | ·                                                                                              |  |

| 15 IOCA2 AO Выход буферного усилителя соs2 (вход АЦП соs2) 16 IS2P AI Прямой вход усилителя sin2 17 IS2N AI Инверсный вход усилителя sin2 18 IOSA2 AO Выход буферного усилителя sin2 (вход АЦП sin2) 19 IC1P AI Прямой вход усилителя cos1 20 IC1N AI Инверсный вход усилителя соs1 21 IOCA1 AO Выход буферного усилителя соs1 (вход АЦП соs1) 22 IS1P AI Прямой вход усилителя sin1 23 IS1N AI Инверсный вход усилителя sin1 24 IOSA1 AO Выход буферного усилителя sin1 (вход АЦП sin1) 25 Tech1 − Технологический вывод 26 Tech2 − Технологический вывод 27 Tech3 − Технологический вывод 28 Tech4 − Технологический вывод 30 VDDA3P3 PWR Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором) 31 VDDD3P3 PWR Вход линейного регулятора напряжения питания цифровой части / вход питания цифровой части (шунтируется конденсатором) 32 VSSA PWR Общий вывод питания аналоговой части Вход линейного регулятора напряжения питания цифровой части / вход питания аналоговой части (шунтируется конденсатором)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13      | IC2P         | Al     | Прямой вход усилителя cos2                                                                     |  |

| 16         IS2P         AI         Прямой вход усилителя sin2           17         IS2N         AI         Инверсный вход усилителя sin2           18         IOSA2         AO         Выход буферного усилителя sin2 (вход АЦП sin2)           19         IC1P         AI         Прямой вход усилителя cos1           20         IC1N         AI         Инверсный вход усилителя cos1           21         IOCA1         AO         Выход буферного усилителя sin1           22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Теch1         —         Технологический вывод           26         Теch2         —         Технологический вывод           27         Теch3         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общи вывод питания аналоговой час                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14      | IC2N         | Al     | Инверсный вход усилителя cos2                                                                  |  |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15      | IOCA2        | AO     | Выход буферного усилителя cos2 (вход АЦП cos2)                                                 |  |

| 18         IOSA2         AO         Выход буферного усилителя sin2 (вход АЦП sin2)           19         IC1P         AI         Прямой вход усилителя cos1           20         IC1N         AI         Инверсный вход усилителя cos1           21         IOCA1         AO         Выход буферного усилителя sin1           22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Tech1         —         Технологический вывод           26         Tech2         —         Технологический вывод           27         Tech3         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16      | IS2P         | Al     | Прямой вход усилителя sin2                                                                     |  |

| 19         IC1P         AI         Прямой вход усилителя cos1           20         IC1N         AI         Инверсный вход усилителя cos1           21         IOCA1         AO         Выход буферного усилителя cos1 (вход АЦП cos1)           22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Tech1         —         Технологический вывод           26         Tech2         —         Технологический вывод           27         Tech3         —         Технологический вывод           28         Tech4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17      | IS2N         | Al     | Инверсный вход усилителя sin2                                                                  |  |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18      | IOSA2        | AO     | Выход буферного усилителя sin2 (вход АЦП sin2)                                                 |  |

| 21   IOCA1   AO   Выход буферного усилителя cos1 (вход АЦП cos1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19      | IC1P         | Al     | Прямой вход усилителя cos1                                                                     |  |

| 22         IS1P         AI         Прямой вход усилителя sin1           23         IS1N         AI         Инверсный вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Tech1         —         Технологический вывод           26         Tech2         —         Технологический вывод           27         Tech3         —         Технологический вывод           28         Tech4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20      | IC1N         | Al     |                                                                                                |  |

| 23         IS1N         AI         Инверсный вход усилителя sin1           24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Tech1         —         Технологический вывод           26         Tech2         —         Технологический вывод           27         Tech3         —         Технологический вывод           28         Tech4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21      | IOCA1        | AO     |                                                                                                |  |

| 24         IOSA1         AO         Выход буферного усилителя sin1 (вход АЦП sin1)           25         Tech1         —         Технологический вывод           26         Tech2         —         Технологический вывод           27         Tech3         —         Технологический вывод           28         Tech4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22      | IS1P         | Al     | Прямой вход усилителя sin1                                                                     |  |

| 25         Tech1         —         Технологический вывод           26         Tech2         —         Технологический вывод           27         Tech3         —         Технологический вывод           28         Tech4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23      | IS1N         | Al     | Инверсный вход усилителя sin1                                                                  |  |

| 26         Tech2         —         Технологический вывод           27         Tech3         —         Технологический вывод           28         Tech4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24      | IOSA1        | AO     | Выход буферного усилителя sin1 (вход АЦП sin1)                                                 |  |

| 27       Tech3       −       Технологический вывод         28       Tech4       −       Технологический вывод         30       VDDA3P3       PWR       Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)         31       VDDD3P3       PWR       Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)         32       VSSA       PWR       Общий вывод питания аналоговой части         33       VDDD       PWR       Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25      | Tech1        | _      | Технологический вывод                                                                          |  |

| 28         Тесh4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26      | Tech2        | _      | Технологический вывод                                                                          |  |

| 28         Tech4         —         Технологический вывод           30         VDDA3P3         PWR         Выход линейного регулятора напряжения питания аналоговой части (шунтируется конденсатором)           31         VDDD3P3         PWR         Вход линейного регулятора напряжения питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27      | Tech3        | _      | Технологический вывод                                                                          |  |

| 30 VDDA3P3 PWR Выход линейного регулятора напряжения питания аналоговой части / вход питания аналоговой части (шунтируется конденсатором)  Вход линейного регулятора напряжения питания цифровой части / вход питания цифровой части (шунтируется конденсатором)  32 VSSA PWR Общий вывод питания аналоговой части  Вход линейного регулятора напряжения питания цифровой части  Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28      | Tech4        | _      | Технологический вывод                                                                          |  |

| 31         VDDD3P3         PWR         части / вход питания цифровой части (шунтируется конденсатором)           32         VSSA         PWR         Общий вывод питания аналоговой части           33         VDDD         PWR         Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |              | PWR    | Выход линейного регулятора напряжения питания аналоговой части / вход питания аналоговой части |  |

| 33 VDDD PWR Вход линейного регулятора напряжения питания цифровой части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31      | VDDD3P3      | PWR    | части / вход питания цифровой части (шунтируется                                               |  |

| 33 VDDD PWR части                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32      | VSSA         | PWR    | Общий вывод питания аналоговой части                                                           |  |

| 35 VPP AI Вывод напряжения программирования                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33      | VDDD         | PWR    | Вход линейного регулятора напряжения питания цифровой                                          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35      | VPP          | Al     | Вывод напряжения программирования                                                              |  |

Обращаем внимание, документация носит ознакомительный характер. При разработке аппаратуры необходимо руководствоваться КД: технические условия АЕНВ.431260.392ТУ, карта заказа КФЦС.431260.041-022Д16.

| Nº     | Наименование | Тип    |                                                                                               |  |

|--------|--------------|--------|-----------------------------------------------------------------------------------------------|--|

| вывода | вывода       | вывода | Назначение вывода                                                                             |  |

| 36, 61 | VDDD1P8      | PWR    | Выход линейного регулятора питания 1,8 В / вход питания ядра (шунтируется конденсатором)      |  |

| 37     | OSCO         | AO     | Вывод подключения внешнего кварцевого резонатора                                              |  |

| 38     | OSCI         | Al     | Вывод для подключения кварцевого резонатора<br>или RC-цепочки                                 |  |

| 39     | CLK60        | Al     | Вход сигнала тактовой частоты от внешнего генератора                                          |  |

| 40     | PLL_CAP      | AO     | Вывод для подключения емкости петлевого фильтра<br>блока PLL                                  |  |

| 41     | DB           | DO     | Вывод отладки режимов и программ<br>Внутренняя подтяжка к VDDIO.                              |  |

| 42     | ENC1_0       | DO     | Выход эмуляции квадратурного энкодера, датчик 1, канал 0.<br>Выход дополнительного канала SPI |  |

| 43     | ENC1_B       | DO     | Выход эмуляции квадратурного энкодера, датчик 1, канал В.<br>Выход дополнительного канала SPI |  |

| 44     | ENC1_A       | DO     | Выход эмуляции квадратурного энкодера, датчик 1, канал А.<br>Выход дополнительного канала SPI |  |

| 45     | VDDIO        | PWR    | Напряжение питания интерфейсной части                                                         |  |

| 46     | ENC2_A       | DO     | Выход эмуляции квадратурного энкодера, датчик 2, канал А.<br>Выход дополнительного канала SPI |  |

| 47     | ENC2_B       | DO     | Выход эмуляции квадратурного энкодера, датчик 2, канал В. Выход дополнительного канала SPI    |  |

| 48     | ENC2_0       | DO     | Выход эмуляции квадратурного энкодера, датчик 2, канал 0.<br>Выход дополнительного канала SPI |  |

| 49     | EXI2         | DI/DO  | Вход/выход опорного напряжения, датчик 2.                                                     |  |

| 50     | EXI1         | DI/DO  | Вход/выход опорного напряжения, датчик 1.                                                     |  |

| 51     | SDO          | DO     | Выход данных SPI                                                                              |  |

| 52     | SDI          | DI/DO  | Вход/выход данных SPI                                                                         |  |

| 53     | VC           | DI/DO  | Выбор режима прямой передачи / управление внешними приемопередатчиками                        |  |

| 55     | SCLK         | DI     | Тактовый сигнал SPI                                                                           |  |

| 56     | NSEN         | DI     | Выбор микросхемы<br>Активный уровень – лог. «0»                                               |  |

| 57     | SSTR         | DI     | Строб SPI                                                                                     |  |

| 58     | STNDBY       | DI     | Режим пониженного энергопотребления:<br>Активный уровень – лог. «1»                           |  |

| 59     | SAMPLE       | DI     | Строб сэмплирования координаты и скорости для SPI                                             |  |

| 62     | NRESET       | DI     | Сброс микросхемы<br>Активный уровень – лог. «0»                                               |  |

| 63     | VDDA         | PWR    | Вход линейного регулятора напряжения питания аналоговой части                                 |  |

| 64     | REFDAC       | AO     | Вход опорного напряжения ЦАП генератора опорной частоты                                       |  |

| EP     | VSSA         | PWR    | Общий вывод                                                                                   |  |