5112НВ035

5112НВ035

14-ти разрядный 50 МВыб/с конвейерный АЦП с параллельным интерфейсом выходных данных

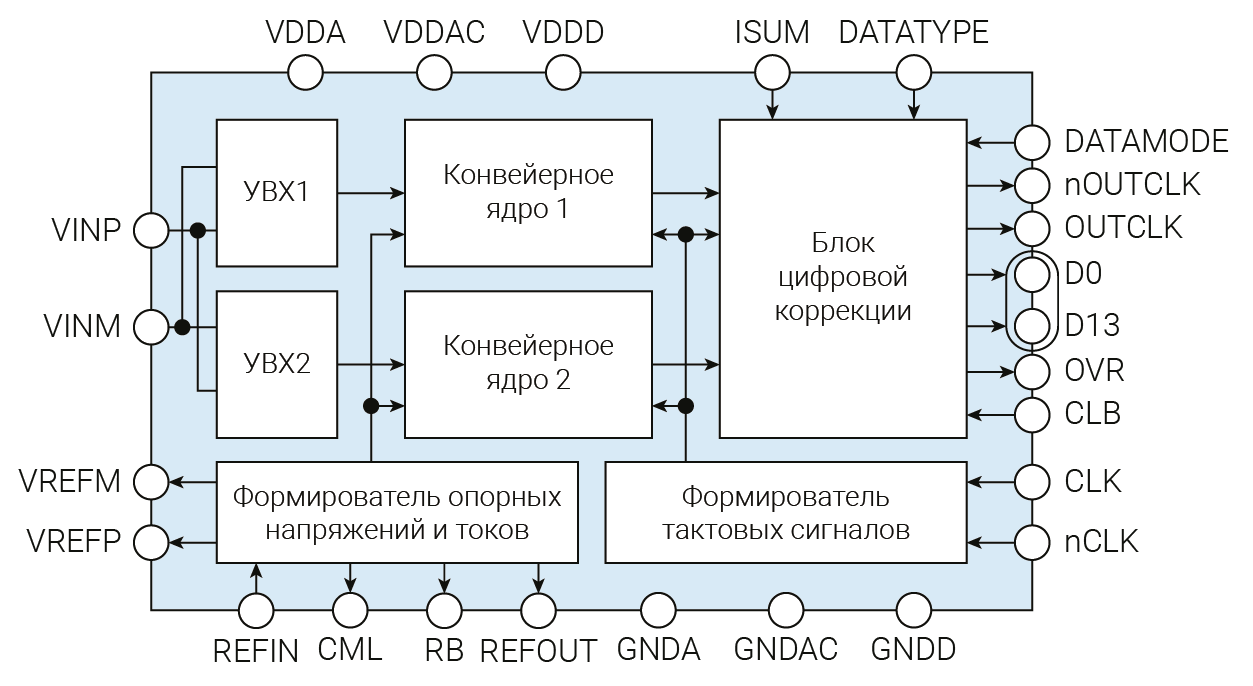

Микросхема 5112НВ035 – 14-ти разрядный АЦП конвейерного типа с параллельным интерфейсом выходных данных (формат: бинарный код со смещением или дополнительный код).

Выходные данные могут быть представлены как КМОП логическими уровнями, так и LVDS. При этом доступно также высокоимпедансное состояние логических выводов.

Возможно использование как встроенного, так и внешнего источника опорного напряжения, значение которого определяет максимальную амплитуду входного сигнала.

АЕНВ.431320.238ТУ

Серийно освоена

Включена в Перечень ЭКБ

Группа А: от –60°С до +125°С

Группа В: от –60°С до +85°С

Характеристики

Разрядность 14 бит

Частота дискретизации 50 МВыб/с

Напряжение полной шкалы 2,0 В

Интегральная нелинейность 3,5 МЗР

Дифференциальная нелинейность 0,6 МЗР

Напряжение входного синфазного сигнала:

• от 1,5 В до 2,4 В (группа А)

• от 2,0 В до 2,2 В (группа В)

Динамический диапазон (SFDR) 80 дБ

Отношение сигнал/шум (SNR) 64 дБ

Напряжение питания 3,15 В ... 3,7 В

_150.png)

_150.png)