5400ВК055

5400ВК055

Сбоеустойчивый 8-ми разрядный контроллер с аппаратной поддержкой интерфейсов UART, SPI, 1-Wire

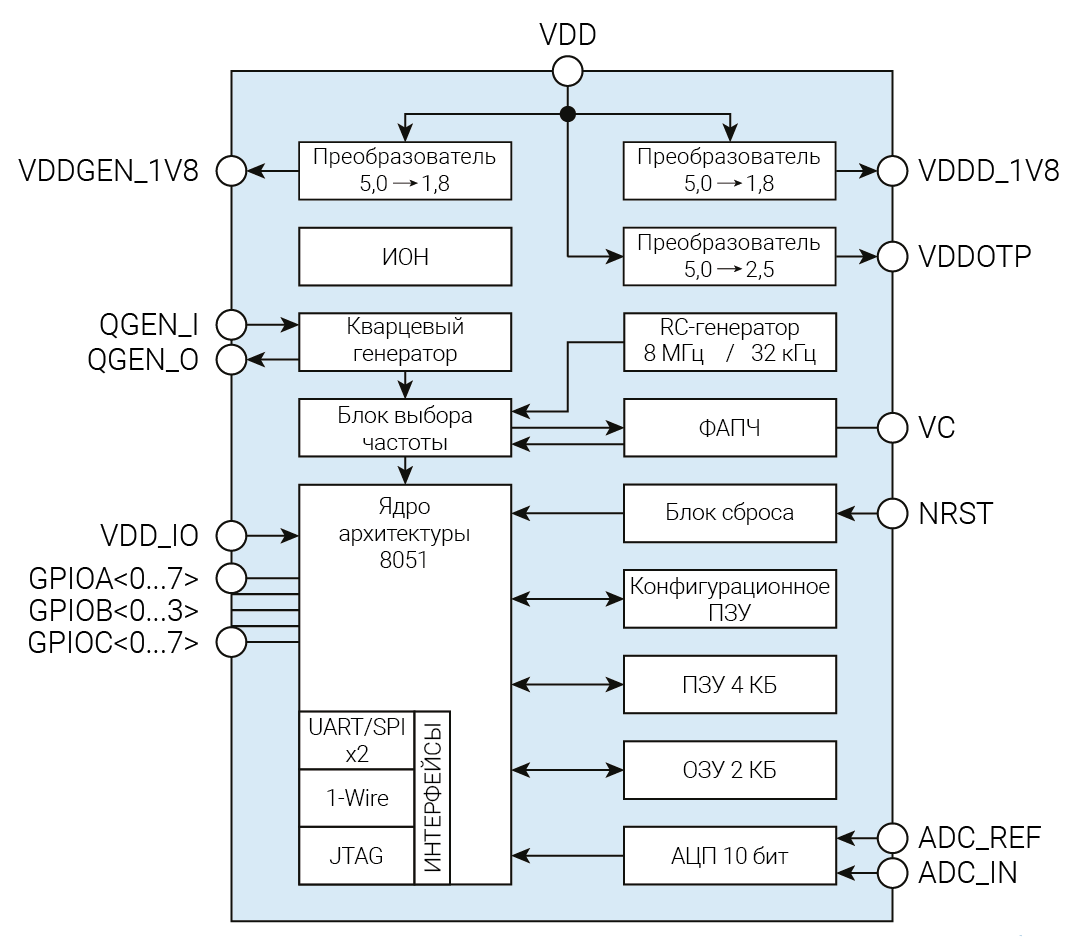

Микросхема 5400ВК055 – контроллер c архитектурой ядра 8051 и диапазоном рабочих частот до 16 МГц (тактирование системы осуществляется несколькими способами: кварцевый резонатор, встроенные высокочастотный (8 МГц) или низкочастотный (32 кГц) RC-генератор, внешний источник, а также путем умножения этих частот с помощью встроенного блока ФАПЧ).

В составе микросхемы до 20 универсальных линий ввода/вывода.

Микросхема работает как в отладочном режиме с возможностью многократного перезаписывания исполняемой программы (до 2 КБ), так и в основном режиме после записи информации в однократно программируемую память (antifuse, до 4 КБ). После программирования микросхема готова к работе при включении питания, времени на загрузку не требуется.

АЕНВ.431290.610ТУ

Опытные образцы

Серийное освоение – 2 квартал 2027 г.

от –60°С до +85°С

В разработке

Характеристики

Напряжение питания 5,0 В ± 5%

Напряжение питания портов ввода/вывода GPIO от 2,5 В до 5,0 В

Динамический ток потребления не более 10 мА (на частоте 8 МГц)

Ядро

Система команд 8051, тактовая частота до 16 МГц

Машинный цикл 1 такт

Возможность выбора способа тактирования:

• кварцевый генератор

• высокочастотный RC-генератор

• низкочастотный RC-генератор

• внешний источник

• ФАПЧ

Контроллер прерываний

Память

Память программ 4 КБ ОППЗУ

Память данных 2 КБ ОЗУ

Работа только с внутренней памятью программ

Периферия

2 контроллера интерфейса UART/SPI

Интерфейс 1-Wire

Интерфейс JTAG (программирование и отладка)

12 универсальных линий ввода/вывода GPIO с индивидуальной настройкой направления

Два 32-разрядных таймера/счетчика

Сторожевой таймер

10-ти разрядный 1 МВыб/с АЦП

RC-генератор с возможностью настройки частоты

Блок ФАПЧ с возможностью настройки коэффициента умножения

Модуль перевода системы в режим пониженного энергопотребления (SLEEP)

Регуляторы напряжения электропитания