Версию статьи, опубликованную в журнале «Электронные компоненты» №4'2026, вы можете прочитать по ссылке.

Компания АО «Дизайн Центр «Союз» получила опытные образцы микросхемы 5400ТР065А-022 – двухканальный преобразователь сигналов индуктивных датчиков трансформаторного типа: сельсин, синусно-косинусный вращающийся трансформатор (СКВТ), линейный регулируемый дифференциальный трансформатор (ЛРДТ). Микросхема разработана на базе радиационно стойкого АЦ БМК и предназначена для преобразования сигналов датчика в код угла или линейной координаты, в том числе в аппаратуре специального назначения.

В настоящее время индуктивные датчики трансформаторного типа (сельсин, СКВТ, ЛРДТ), преобразующие механическое перемещение в электрический сигнал, сохраняют широкое применение в разных областях деятельности благодаря надежности и способности работать в сложных условиях эксплуатации. Эти устройства используются для измерения угловых и линейных перемещений, что востребовано в промышленности, авиации, робототехнике и других сферах. Датчики в своем составе содержат как механическую часть, так и электронную – для обработки сигналов, генерации возбуждающего напряжения, преобразования данных. С развитием датчиков электронная часть все чаще реализуется с помощью специализированных микросхем, позволяющих генерировать синусоидальное напряжение для возбуждения датчиков, преобразовывать аналоговые сигналы с обмоток в цифровой код угла, компенсировать погрешности, реализовывать следящие контуры с обратной связью для повышения точности и устойчивости к помехам и выдавать результаты в удобном цифровом формате.

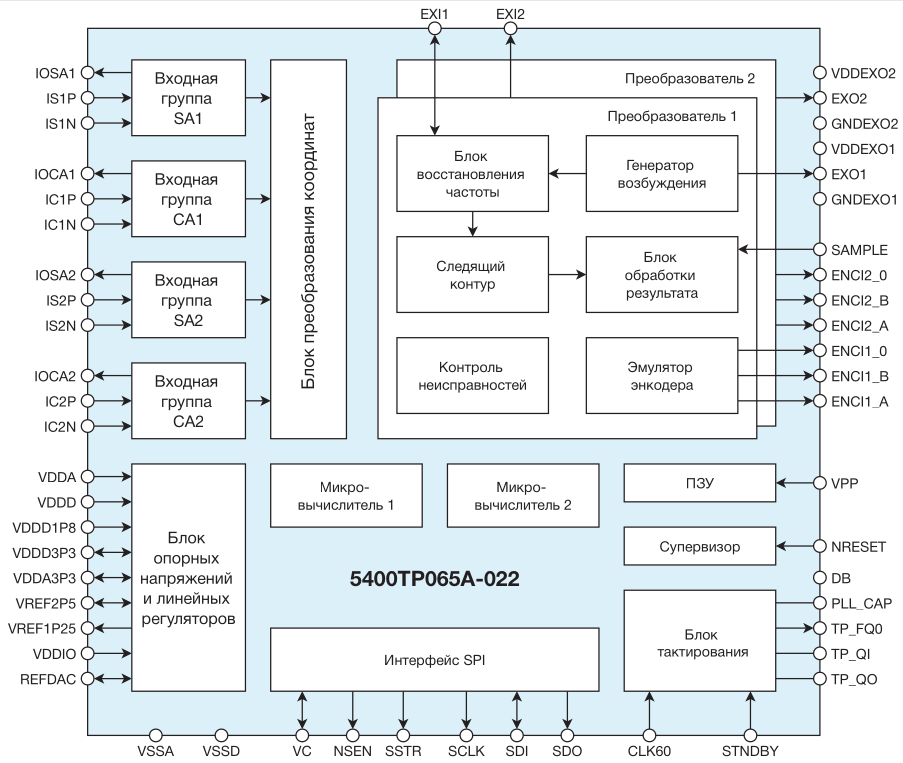

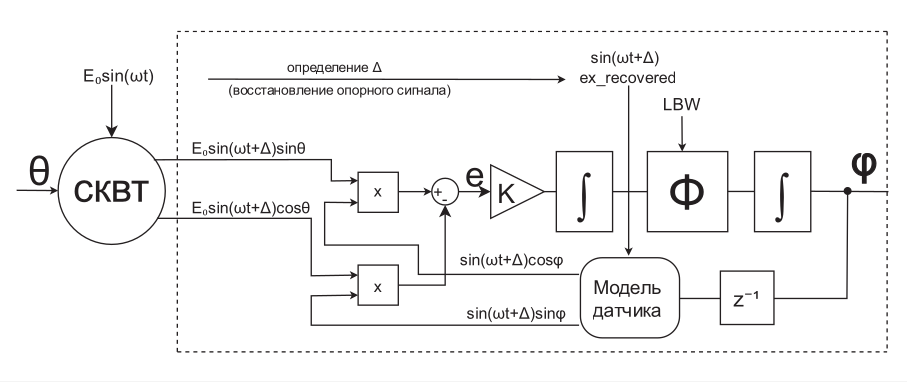

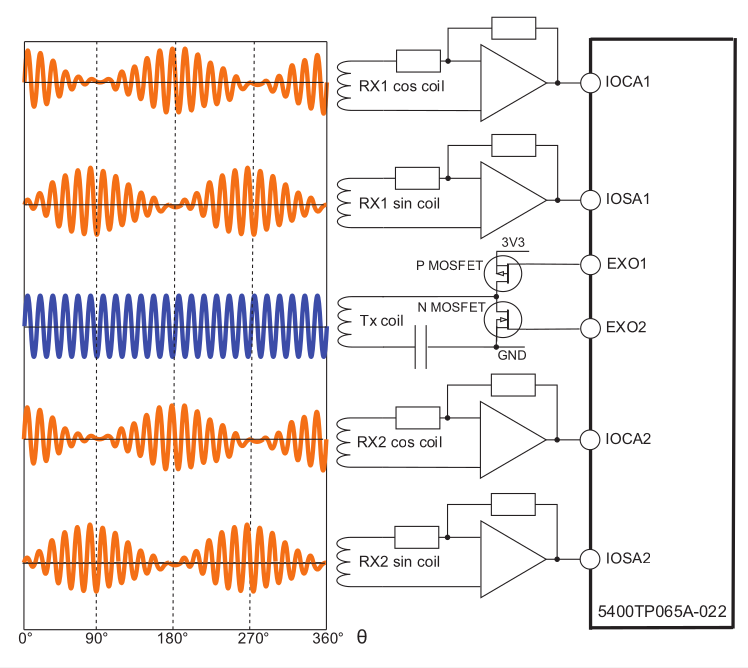

В микросхеме 5400ТР065А‑022 (рис. 1) реализованы два независимых канала. В основу архитектуры положен следящий контур с астатизмом 2‑го порядка, что является традиционным решением для электронных блоков датчиков этого типа (рис. 2). Для работы контура не требуется выпрямление сигналов СКВТ; при расчете углового положения используется весь набор выборок АЦП переменного сигнала на частоте возбуждения датчика. Отсутствие выпрямителей позволяет формировать полосу расчета выходного угла выше полосы возбуждения, что важно при использовании низкочастотных датчиков (до 1 кГц) в электроприводах. Соотношение между быстродействием контура и уровнем выходного шума задается параметром LBW (4 бит), позволяющим выбирать между числом эффективных разрядов и динамикой регулирования.

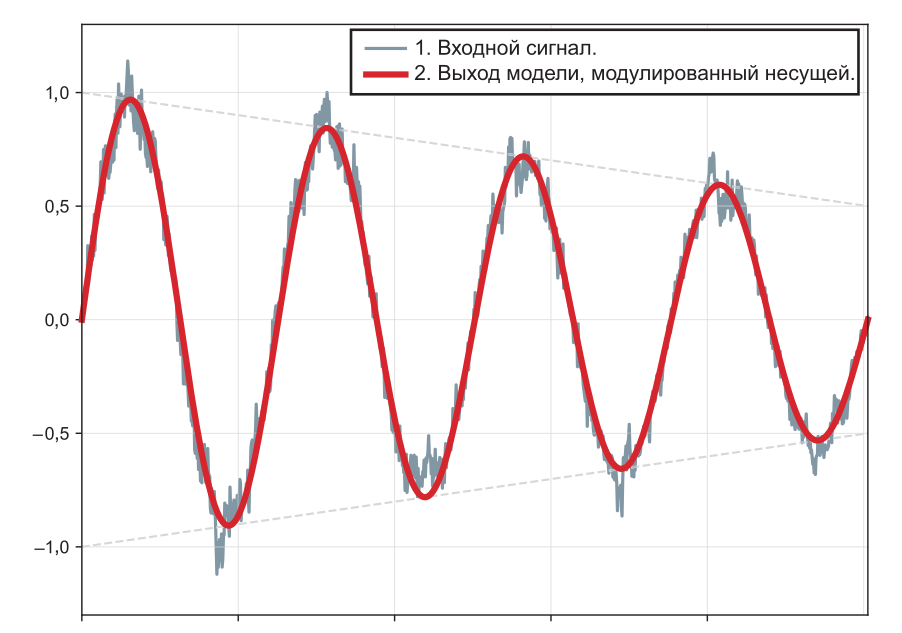

Работа контура основана на минимизации разности между сигналами модели датчика и реальными входными сигналами (рис. 3). Параметры модели определяют уровень первичного шума в контуре и, как следствие, точность выходного угла. В 5400ТР065А‑022 предусмотрена буферизация не только отсчетов АЦП, но и промежуточных данных конвейера обработки, включая сигналы модели датчика. Это упрощает подбор коэффициентов и настройку преобразователя для датчика конкретного типа.

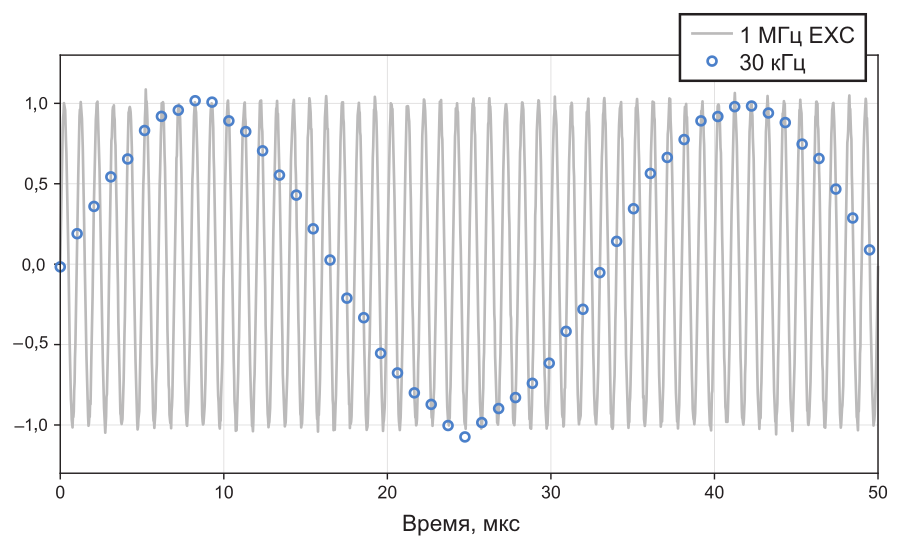

В микросхеме реализован программный сдвиг фазы опорного сигнала (EXI1, EXI2) независимо от источника возбуждения (внутренний или внешний генератор). Постоянная задержка задается 16‑бит параметром в тактах работы контура. Контроль фазового соответствия осуществляется путем передачи в инструментальное ПО оцифрованных значений входных сигналов АЦП, а также первичной и сдвинутой опоры. Входной тракт рассчитан на работу с сигналами до 50 кГц, а также предусмотрен режим прямой оцифровки сигналов до 5 МГц, предназначенный для датчиков на печатных обмотках. В этом режиме используется стробоскопический перенос высокочастотного сигнала в область до ~30 кГц с последующей обработкой следящим контуром (рис. 4).

Генератор возбуждения построен с использованием опорного напряжения АЦП для формирования сигнала ЦАП возбуждения с возможностью корректировки амплитуды, что обеспечивает масштабный температурный дрейф и его взаимную компенсацию.

Предусмотрен режим генерации меандра до 5 МГц для управления внешней комплементарной печатных обмотках с заданными требованиями по точности, разрешению и конструкции (рис. 6).

Для повышения гибкости применения при построении конкретных датчиков микросхема 5400ТР065А‑022 заключает в себе два специализированных микровычислителя. Каждый из них содержит 232 ячейки памяти (общей для команд и данных), 8 регистров общего назначения разрядностью 28/56 бит и набор из 56 14‑бит ассемблерных инструкций, включая умножение с накоплением и операции с коэффициентами с плавающей запятой. Применение двух вычислителей и выбранная разрядность обусловлены необходимостью вычисления угла и его производных с периодом 40–120 мкс, соответствующим типичному циклу формирования ПИД-управления электроприводом.

Разработка пользовательских программ на ассемблере возможна с помощью средств автоматической генерации кода на основе контекста описания архитектуры микровычислителей и примеров кода. Проверка микропрограмм возможна в системной модели на SystemVerilog в выбранном симуляторе либо аппаратно – в режиме пошаговой отладки по SPI с выводом содержимого регистров и ОЗУ (предусмотрены две точки останова).

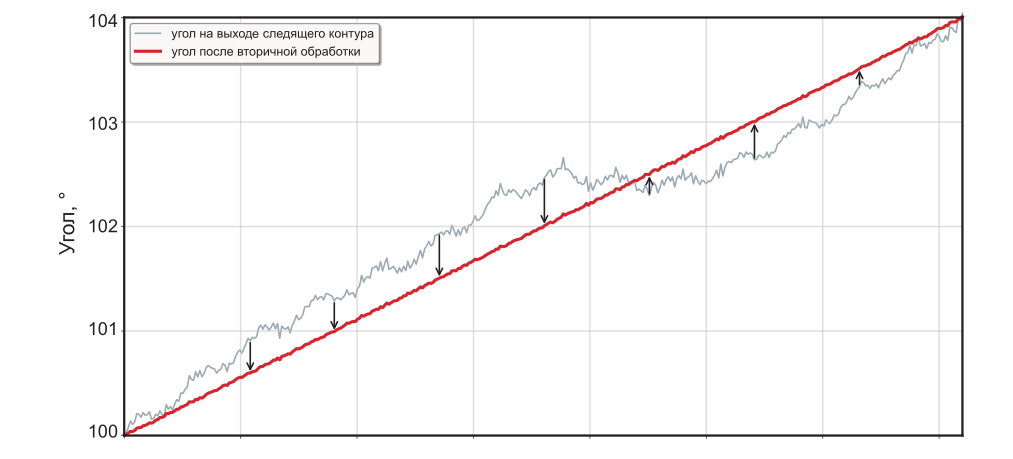

Пример применения микровычислителей: в первом из них реализована программа корректировки грубого отсчета по шести гармоникам, согласование отсчетов (три грубых к восьми точным) и последующий циклический расчет интерполирующей квадратичной функции методом наименьших квадратов по окну из 63 точек с вычислением 1‑й и 2‑й производных на конце интервала. Во втором микровычислителе выполняется циклический расчет и коррекция систематической погрешности полного угла с использованием обратного дискретного преобразования Фурье по 32 гармоническим коэффициентам (рис. 7).

Применение 5400ТР065А‑022 позволяет перенести низкоуровневую обработку сигналов с управляющего контроллера на специализированную микросхему.

Наличие встроенной энергонезависимой памяти сокращает время ввода аппаратуры в работу после подачи питания или сигнала сброса. Предусмотрена адресация до 255 устройств на одной линии SPI, а также специальный вывод для управления приемом и передачей внешними микросхемами дифференциальных интерфейсов RS‑485 и M-LVDS.

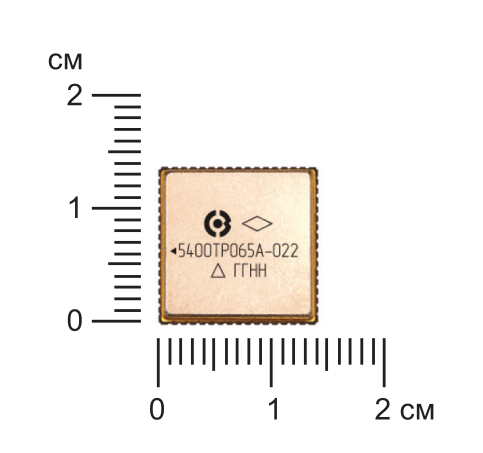

Микросхема выполнена в 64-выводном металлокерамическом корпусе МК 5153.64-3 с размерами 13,8×13,8 мм (рис. 8) и предназначена для работы в широком температурном диапазоне –60…125°C. В настоящее время получены опытные образцы, ведется серийное освоение с приемкой «ВП» с плановым сроком завершения в III кв. 2026 г.

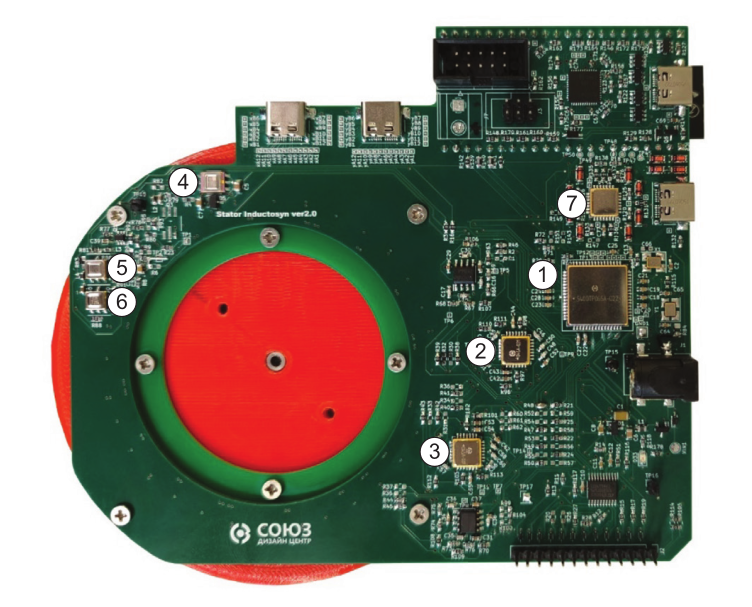

Для оценки характеристик разработан отладочный комплект КФЦС.441461.448, который предназначен для демонстрации функциональных возможностей микросхемы.

Микросхема 5400ТР065А‑022 обладает высокой надежностью (наработка до отказа – свыше 100 тыс. ч) и стойкостью к СВВФ, включая факторы космического пространства (стойкость к ТЗЧ – не менее 60 МэВ·см2/мг).

Сочетание аналоговой точности и функциональных возможностей делает эту микросхему надежной основой для разработки отечественных измерительных комплексов в сфере специального приборостроения и промышленной электроники.